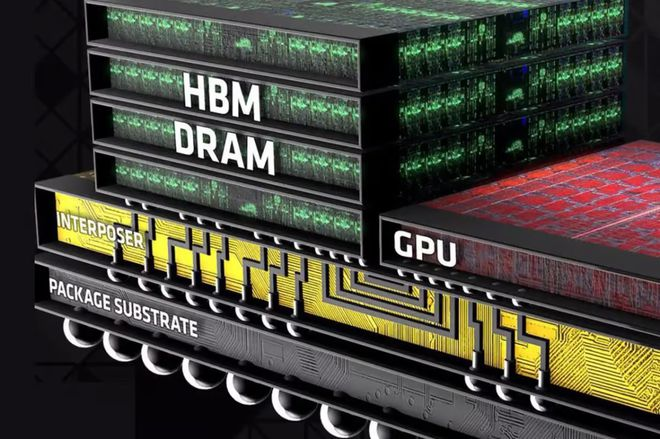

近日,英伟达传出将进入HBM base die市场,引发业界广泛关注。据悉,英伟达计划自研HBM(高频宽存储器)Base Die,制程节点锁定3nm,预计将于2027年下半年开始小量试产。此举意在提升HBM与GPU、CPU数据传输的顺畅性,为客户提供更多模块化选择,进一步强化其NVLink Fusion开放架构生态系的掌控力。

目前,HBM市场主要由DRAM大厂主导,其中SK海力士占据最高市占率。然而,随着HBM传输速度要求提升至10Gbps以上,制程难度也随之增加,需借助台积电等先进制程技术。据悉,HBM4以上传输速率要求达到10G以上,需以先进制程打造Logic die,因此会委由台积电制作,而ASIC部分则由创意负责。创意的HBM4 IP支持高达12Gbps数据传输速率,并纳入32Gbps UCIe-A及UCIe-3D IP等解决方案,处于业界领先地位。

英伟达的入局被视为对ASIC市场的挑战,但其解决方案被CSP大厂采用的可能性不高。业界分析,CSP大厂投入ASIC正是为了避免受制于英伟达,因此对其HBM Base Die的接受度有限。不过,英伟达的模组化设计有望使联发科、世芯等合作伙伴受益,获得更多商机。

整体来看,HBM4世代将迎来更高速、更高堆栈、更复杂封装整合的新局面。随着英伟达拟自制Base Die与SK海力士加速HBM4量产,HBM市场将迎来新一波竞争与变革。