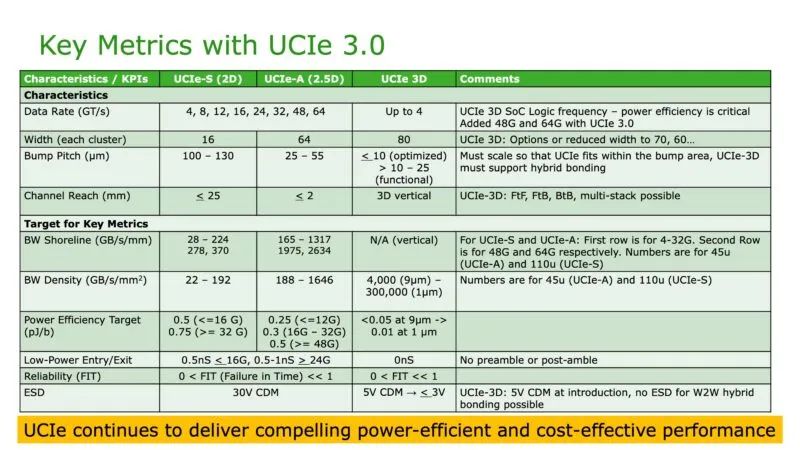

8月6日,全球开放芯粒(Chiplet)互连标准组织UCIe(Universal Chiplet Interconnect Express)联盟正式发布了其最新版本的UCIe 3.0规范。这一规范的发布标志着芯粒行业在数据传输速率和能效优化方面迈出了重要一步。

UCIe 3.0规范将数据传输速率提升至64 GT/s,较上一代UCIe 2.0的32 GT/s实现了带宽翻倍。新规范通过引入多项关键技术,旨在提升多芯片系统封装(SiP)设计的能效与灵活性,进一步推动Chiplet技术在AI、数据中心及高性能计算领域的应用。

新规范的核心亮点包括运行时重校准(Runtime Recalibration)和扩展边带传输(Extended Sideband Transmission)。运行时重校准通过动态调节链路参数,降低动态功耗,提升整体能效;扩展边带传输则将边带信道长度扩展至100毫米,支持更灵活的多芯片拓扑结构,为异构集成提供更大设计自由度。

此外,UCIe 3.0还引入了连续传输协议(Continuous Transmission in Raw Mode),适用于实时性要求高的场景,如AI推理和5G通信。同时,新规范强化了系统管理功能,包括优先级边带数据包、预载固件标准化以及快速节流与紧急关断机制,确保系统在突发情况下的快速响应。

UCIe 3.0规范完全后向兼容此前所有版本(UCIe 1.0至UCIe 2.0),并采用可选管理功能模块化设计,允许企业根据需求选择性实现特定功能,降低设计复杂度和资源浪费。

UCIe联盟主席兼三星电子高级副总裁Cheolmin Park表示:“UCIe 3.0是芯粒行业发展的关键一步。通过提升带宽密度、优化能效和增强系统管理,我们为开发者提供了构建高性能、高灵活性SiP解决方案的基础。”

UCIe 3.0的发布将直接影响多个技术领域。在AI与高性能计算(HPC)领域,更高的数据速率和连续传输能力可显著提升AI芯片的算力效率;在5G与通信设备领域,扩展边带传输和优先级信令功能可优化基站芯片的信号处理能力;在汽车电子领域,模块化设计将帮助车企灵活集成不同供应商的芯片,缩短开发周期并降低成本。

Synopsys等EDA工具厂商已宣布推出支持UCIe 3.0的IP解决方案,预计2026年将有首批基于该规范的芯片进入设计阶段。据TechPowerUp报道,部分厂商推测UCIe 3.0芯片可能于2028-2029年量产。

此次UCIe 3.0规范的发布,不仅是对前代规范的延续和提升,更是对整个芯粒生态系统的一次重要革新。随着技术的不断进步和应用场景的拓展,UCIe 3.0有望在未来几年内成为推动AI、高性能计算及通信设备等领域发展的关键力量。