全球RISC-V芯片出货量已突破百亿,其开源、免费的特性及“乐高式”模块化设计赋予开发者前所未有的自由,可灵活组合指令集,打造从物联网到AI加速器的全场景芯片。吸引了全球众多企业、科研机构和开发者的参与,中国更是坐拥最大应用市场和最活跃的开发者社区,推动该架构强势崛起。

然而,国内RISC-V发展的关键瓶颈已然显现——电子设计自动化(EDA)工具的缺失。正如芯华章科技技术总监所言:“RISC-V开启了芯片设计的定制化时代,但我们的EDA工具仍停留在流水线阶段。”

这种工具能力与架构潜力之间的巨大鸿沟,揭示了问题的核心。它要求从封闭的单向流程转向开放的协同生态,从对标准工艺的被动适配转向对定制场景的主动优化,从单点技术的零散突破转向全系统层面的深度创新。

破局需提升四大核心能力

RISC-V架构的模块化特征,即基础指令集与扩展指令的组合模式,对EDA工具提出了多维度的技术要求。

其一,需高效支持用户自定义指令(Custom Instructions)的开发,以及微架构优化的快速验证与落地实现;其二,面对碎片化配置引发的验证空间爆炸问题,工具链需具备处理海量组合场景的能力,涵盖不同扩展指令集的组合验证、多核一致性验证等复杂场景;其三,编译器、操作系统与硬件的深度协同优化,依赖EDA工具提供高效的虚拟原型(Virtual Prototype)及早期性能分析能力,以支撑全系统层面的设计迭代;其四,从物联网到数据中心的全场景应用中,芯片内建安全机制(如内存加密、信任根等)的需求日益凸显,要求 EDA 工具支持安全架构的自动化设计与验证流程。

基于上述需求,国内EDA厂商需重点提升四大核心能力。

从产业价值而言,全流程自主工具链是摆脱对外依赖、保障 RISC-V生态自主可控的核心支柱。只有实现从RTL设计、功能验证、物理实现到签核的全流程工具自主可控,才能避免在RISC-V芯片设计的关键环节受制于外部工具壁垒,确保定制化创新的自由度与安全性。

在提升RISC-V专用增强能力上,国内EDA工具要突出针对性。要能自动完成自定义指令的识别、RTL生成及编译器集成,加快算法到硬件的转化;要有类似Codasip Studio的国产可配置处理器生成平台,实现 “勾选式” 生成RISC-V SoC,降低设计门槛;还要搭建异构计算验证平台,解决RISC-V核与GPU、AI加速器的协同仿真及跨域通信问题。

系统级设计能力的强化,需重点构建两大核心技术支撑:一方面,需打造基于QEMU/SystemC的虚拟原型开发环境,通过早期建模实现软件调试流程的前置化,例如借鉴龙芯LoongArch架构的虚拟化经验,支持在Linux系统启动前完成80%以上的软件调试工作,大幅缩短软硬协同开发周期;另一方面,需具备RTL阶段的功耗与性能预测能力,参考Ansys PowerArtist等工具的技术路径,实现芯片PPA(性能、功耗、面积)指标的精准预判,从而减少后端设计环节的迭代次数,提升整体设计效率。

生态协同能力的提升,关键在于构建开放的接口标准。需打造具备国产自主特性的开放API(如Python/TCL接口),通过标准化的接口设计,实现与主流生态的兼容互通,既能够无缝集成KLayout、OpenROAD等开源EDA工具,也能为第三方开发者提供灵活的二次开发基础,从而打破工具间的壁垒,形成协同高效的生态体系。

事实上,国内EDA厂商在RISC-V领域已有不少进展。合见工软的验证系统支撑了“香山”等RISC-V处理器的高效验证,实现多核系统快速调试,还推出新一代工具提升早期设计效率;汤谷智能研发出AI驱动的前端设计验证工具,构建了覆盖从RTL到版图的全流程工具链,其原型验证产品支持大规模设计,并参与建设开源芯片服务平台;芯华章的验证平台在RISC-V处理器验证中提升了调试能力和效率;思尔芯则通过IP评测助力RISC-V生态建设。

这些成果都为为国内RISC-V芯片设计提供了实用工具支持。

并购整合打破“小而散”格局

近期,新思科技以350亿美元完成对仿真EDA公司Ansys的收购,这一并购对RISC-V发展意义重大。

收购前,新思科技在RISC-V领域已有布局,而Ansys在仿真与分析产品组合方面优势显著。收购完成后,双方优势融合,加速补全RISC-V设计全流程工具链。例如,在架构仿真环节,利用Ansys的多物理场仿真技术,能让开发者更精准地模拟RISC-V架构在不同场景下的性能表现,提前优化设计;在硬件验证阶段,结合新思科技原有的验证工具与Ansys的分析能力,可高效检测出硬件设计中的潜在问题,大幅提升从架构仿真到硬件验证的效率。

同时,新思科技积极将收购来的技术与自身生态及开源社区深度协同。新思科技拥有庞大的客户群体和完善的生态体系,通过将Ansys技术融入其中,能为RISC-V开发者提供更全面、便捷的开发环境,降低使用门槛。在开源社区方面,新思科技会基于收购技术,开发适配RISC-V开源社区的工具插件或模块,促进社区内开发者交流与合作,加速RISC-V芯片在嵌入式、高性能计算等场景的落地,推动全球RISC-V生态从技术探索迈向产业化应用的新阶段。

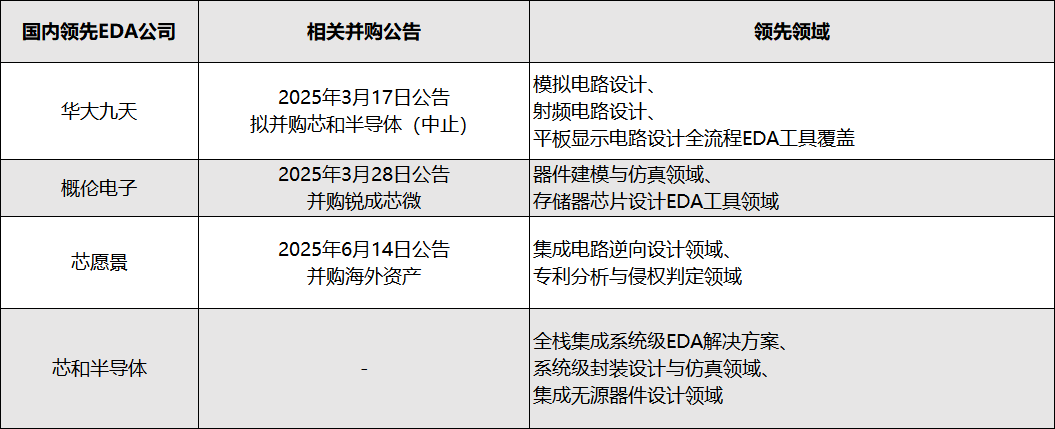

2025年上半年,国内EDA行业也同样在延续近年来的整合趋势,加速技术整合、拓展产品线、提升综合竞争力的战略方向,为RSIC-V的规模化应用保驾护航。

在RISC-V领域,验证环节尤其是硬件加速验证,是国内全流程EDA厂商亟待攻克的关键领域。思尔芯在这方面技术底蕴深厚,其产品能显著提升芯片验证的效率与精度,足以应对复杂芯片设计的严苛要求。

2025年,概伦电子以现金加股权的方式,完成了对思尔芯(S2C)的100%收购。此前,概伦电子在SPICE仿真器(NanoSpice)、良率分析(Yield Explorer)、建模与测试(BSIMProPlus)等点工具上实力强劲,但在验证环节稍显薄弱。而思尔芯在FPGA原型验证和硬件加速仿真领域处于全球领先,在中国市场份额颇高。此次收购,极大地增强了概伦电子在数字电路设计和验证后端的能力,补齐了产品线短板,在RISC-V处理器设计中,可借助思尔芯技术加速验证流程,快速排查设计漏洞,确保指令集扩展、多核架构协同等关键设计的正确性,助力RISC-V芯片高效迭代。

国内厂商也将目光投向海外,寻求优质资产并购以提升技术实力。2025年3月,专注芯片分析(逆向工程/ IP分析)和设计服务的芯愿景,收购了一家海外EDA公司的特定点工具资产组合。芯愿景意在补充芯片分析服务所需的核心EDA技术栈,提升技术壁垒与自动化能力。RISC-V 生态发展迅速,对芯片分析技术要求渐高,获取这些特定点工具技术后,芯愿景有望将服务能力向RISC-V芯片正向设计支持延伸,或拓展至更专业的分析领域,如精准解析RISC-V定制指令集在芯片中的运行逻辑,为RISC-V芯片优化设计、提高性能可靠性提供关键技术支撑 。

备受瞩目的华大九天收购芯和半导体科技(上海)股份有限公司控股权案,虽然已于7月9日宣告终止,但华大九天在并购整合及产业投资方面的布局仍在持续推进。上市以来,公司已收购芯达芯片科技有限公司,投资了上海阿卡思电子技术有限公司等多家企业,并携手专业投资机构共同设立了两只产业基金。

芯和半导体同样是一家优秀的专注于EDA软件工具研发的高新技术企业,在射频、高速、多物理场仿真等领域技术优势显著,其开发的多物理引擎技术,能提供从芯片到整机系统的全栈集成系统EDA解决方案,支持Chiplet先进封装。

从国内EDA公司上半年的并购动态中,可清晰洞察行业发展的深层趋势与核心诉求:EDA企业完善业务布局的迫切性。当前国内EDA行业虽企业数量众多,但营收规模过亿元的主体较少,整体呈现“小而散”的格局。通过并购整合,企业能够实现技术、人才与市场资源的高效协同,打破分散化发展的瓶颈;更重要的是,这种整合推动产业链加速构建自主可控的工具生态联盟,减少对单一外部工具的依赖,为中国RISC-V芯片从架构创新走向规模化落地夯实工具链根基,助力其在定制化指令开发、多核验证等关键环节形成自主可控的技术闭环。