近日,功率半导体器件领域的顶级会议IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD) 在日本熊本市举行。北京大学集成电路学院两篇高水平论文入选,向国际功率器件与功率集成电路领域的同行展示了北京大学最新的研究成果。这两篇论文内容涉及GaN CMOS集成技术、SiC MOSFET可靠性物理研究。论文详情如下:

1 高性能GaN CMOS集成技术

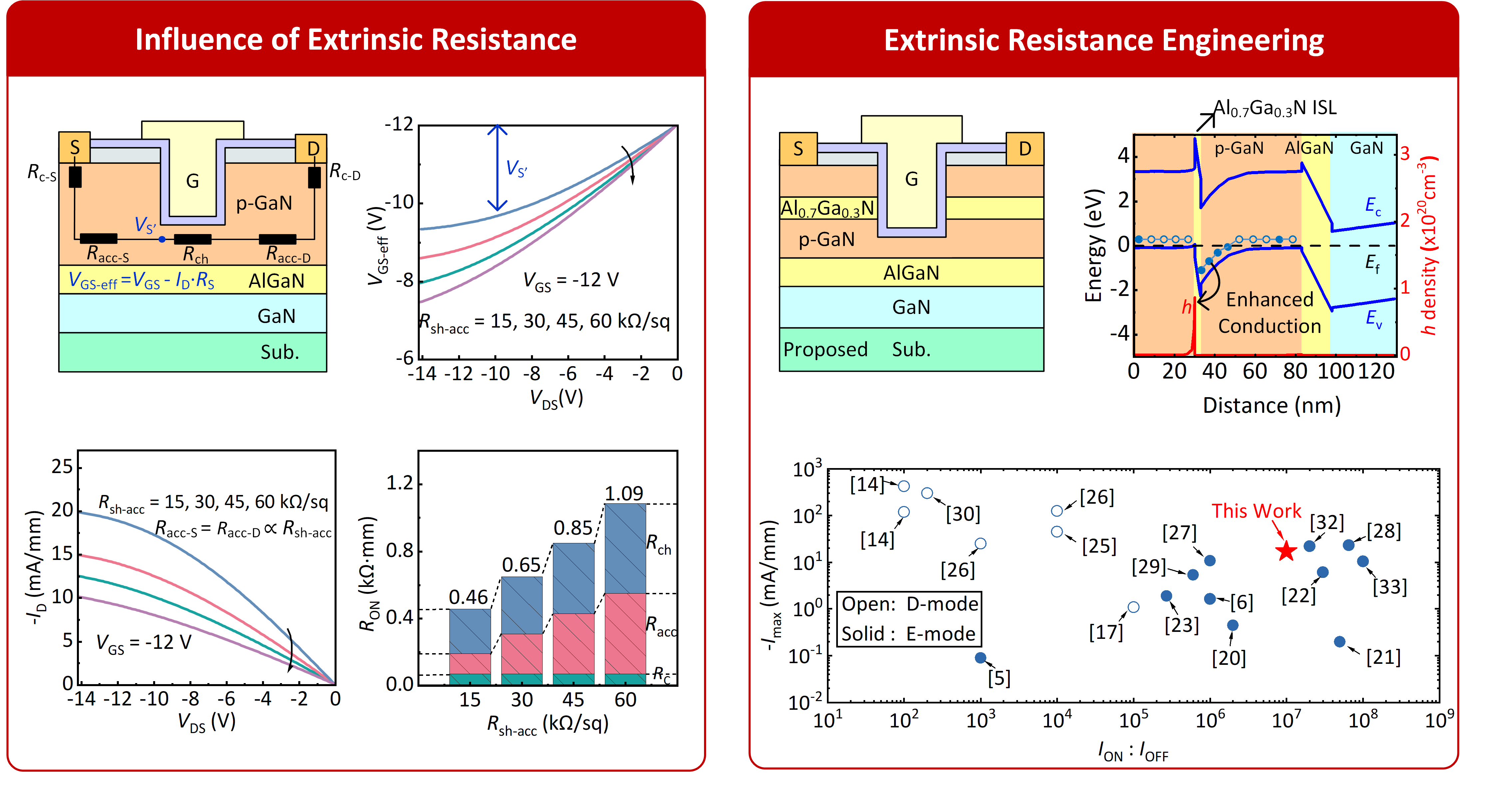

GaN CMOS逻辑电路是提升GaN功率芯片高频特性的重要技术环节。然而,当前GaN p沟道场效应管 (p-FET) 的低电流密度问题限制了该技术的发展。针对这一问题,当前多数研究聚焦于器件沟道区域的优化,然而,p-FET低电流密度问题仍未得到有效解决。

北京大学魏进团队研究发现源极电阻对电流密度具有重要的影响。首先,研究团队通过TCAD仿真发现源极电阻降低器件沟道处的有效栅压,从而降低器件电流密度和增大器件的沟道电阻。为优化器件源极电阻从而提升电学性能,该团队通过在器件接入区域插入一层Al0.7Ga0.3N,利用电离增强的方案有效降低器件的源极电阻。器件测试结果验证了通过源极电阻工程可有效提升GaN p-FET电流密度,测试数据处于国际先进水平。相关成果以Engineering Extrinsic Resistance of E-Mode GaN p-FET towards Enhanced Current Density为题,发表于2025年国际功率半导体器件与集成电路研讨会 (ISPSD), 文章第一作者是北京大学集成电路学院博士研究生段嘉霖,通讯作者是魏进研究员。

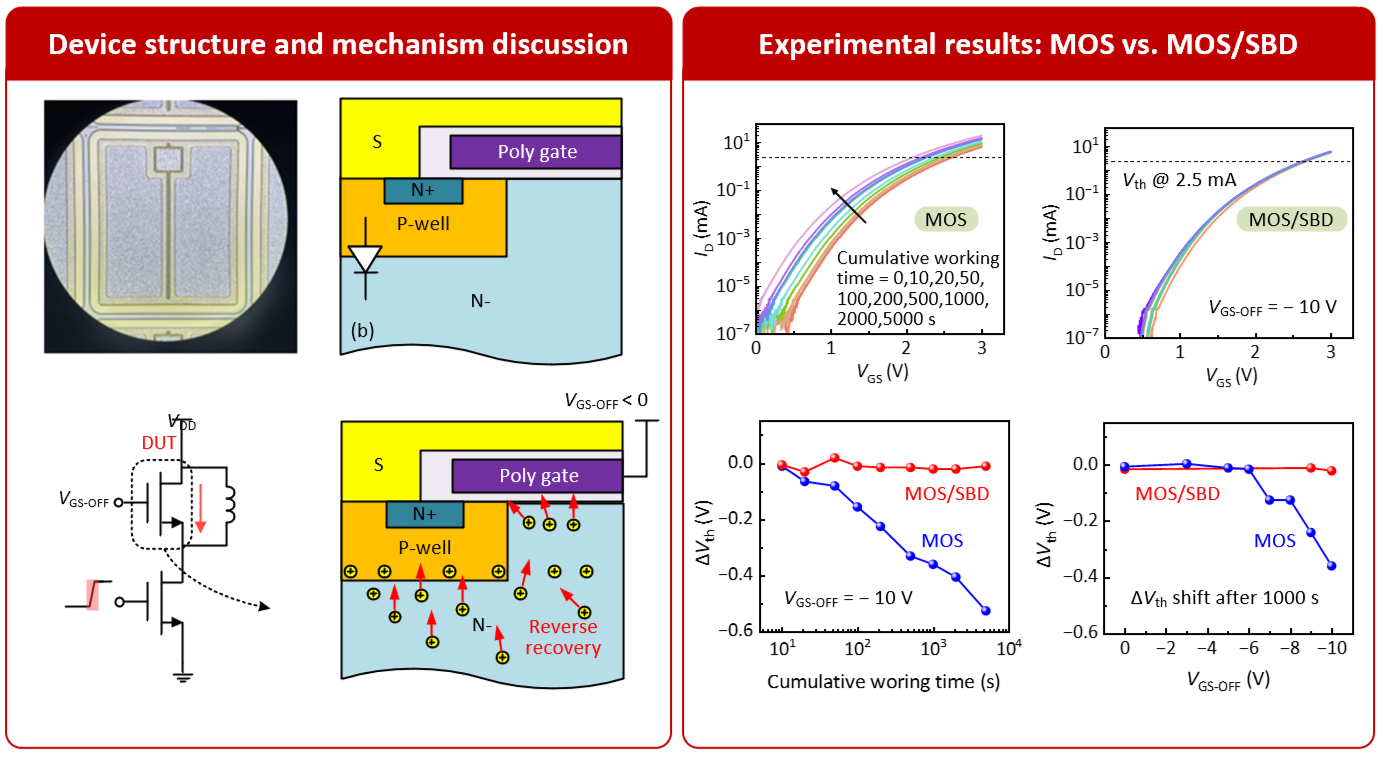

2 一种SiC MOSFET阈值电压负漂移新机制研究

目前,SiC功率器件已在商业领域取得重大成功,但受限于当前的氧化工艺导致的较高界面陷阱,以及SiC/SiO₂界面较小的带隙差,使得阈值电压Vth不稳定性成为SiC MOSFET的一个突出难题。在同步整流等实际应用场景中,续流二极管是必不可少的元件。一方面,相比反并联肖特基势垒二极管 (SBD),SiC MOSFET内置的体二极管凭借其更高的成本效益展现出显著优势。另一方面,为了抑制SiC MOSFET误开启现象,常使用负的栅极电压将器件关断。北京大学魏进研究员团队通过深入研究首次发现,在体二极管导通状态下施加负的栅极电压关断器件时,会引发显著的阈值电压负漂移现象。

针对这一重要发现,研究团队创新性地提出了一种全新的物理机制:当体二极管导通时,p-well区会向JFET区注入大量空穴;在反向恢复过程中,这些空穴在漏极电场作用下加速流向源极,其中部分空穴被加在栅极上的负压吸引,通过轰击栅氧,在栅氧化层中积累固定的净正电荷,导致阈值电压漂移。该物理机制首次系统揭示了负栅偏压诱导的阈值电压不稳定性与体二极管导通的关联性。该研究以Negative Gate Bias Induced Vth Instability in SiC MOSFET: Role of Body Diode Conduction为题,发表于2025年国际功率半导体器件与集成电路研讨会ISPSD。文章的共同第一作者为北京大学/北京工业大学联合培养硕士生王珮瑄和北京大学博士生劳云鸿,通讯作者为魏进研究员。