通用芯粒互连技术(UCIe)为半导体行业带来了诸多可能性,在Multi-Die设计中实现了高带宽、低功耗和低延迟的Die-to-Die连接。它支持定制HBM(cHBM)等创新应用,满足了I/O裸片与HBM DRAM堆叠裸片之间对高带宽连接的需求。本文将深入探讨UCIe支持的不同接口,以实现片上网络(NoC)互连。

UCIe标准层

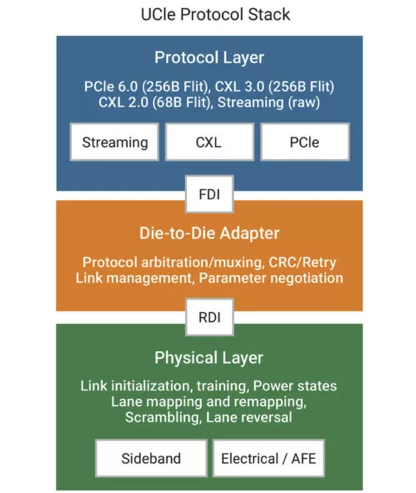

UCIe定义了一套全面的协议层,用于标准化裸片(也称为芯粒)之间的通信。该标准确保数据能够高速传输,同时将延迟和功耗降至最低。如图1所示,UCIe包括三层:

物理(PHY)层:管理UCIe链路的物理特性。该层由模拟前端构成,负责主链路训练与初始化、边带初始化和训练,以及通道修复、重新校准、时钟转发等功能。

Die-to-Die适配层:实现较低的链路层功能。它负责循环冗余校验(CRC)的嵌入和检查、FLIT重传,以及与PHY层的链路状态管理和参数协商。该层还包含用于连接到上层接口的协议仲裁逻辑。

协议层:通过可连接SoC片上网络(NoC)的不同协议和接口(包括AXI、CXS、CHI C2C接口以及PCIe和CXL协议),与SoC应用进行通信。UCIe标准定义了用于连接SoC NoC的串流原生和串流FLIT接口。

图1:UCIe规范层

串流FLIT是指通过Die-to-Die接口发送的数据被打包成FLIT,这些FLIT由PCIe和CXL协议定义。UCIe标准定义了六种FLIT格式:

格式1:64B原始数据,无CRC或重传字节

格式2:68B FLIT,包含64B有效载荷、2B CRC,以及由Die-to-Die适配器填充的2B标头数据

格式3:256B FLIT,包含240B数据有效载荷、16B CRC,以及由Die-to-Die适配器填充的标头

格式4:256B FLIT,包含240B数据有效载荷、16B CRC,以及由Die-to-Die适配器填充的起始标头

格式5:延迟优化的256B FLIT,无可选字节,包含236B有效载荷、20B CRC,以及由Die-to-Die适配器填充的标头数据

格式6:延迟优化的256B FLIT,含可选字节,包含250B有效载荷、6B CRC,以及由Die-to-Die适配器填充的标头数据

格式2到6允许为CRC重传和标头分配字节,Die-to-Die适配器利用这些字节实现近乎无错的链路。

在串流原生模式下,Die-to-Die适配器不会将应用数据转换为FLIT。此模式在逻辑上将PHY RDI接口连接到应用层,提供了Die-to-Die互连的最低延迟路径。

新思科技UCIe控制器IP在协议层中支持多种与SoC应用层的接口,例如CXS、AXI和CHI C2C。这些接口基于Die-to-Die适配器的串流FLIT模式实现,这意味着它们采用UCIe标准中定义的FLIT格式之一。

封闭式与非封闭式Multi-Die设计

根据具体的应用,系统可以采用上述任何一种Die-to-Die接口类型。

开发者必须明确Multi-Die设计是否为封闭式。封闭式Multi-Die设计是指来自同一供应商的裸片通过Die-to-Die IP进行互操作。在这种情况下,由同一供应商负责裸片之间的数据连接。这种应用场景在业界较为常见,许多公司在设计系统时会在自家的其他裸片中添加功能或进行扩展。

封闭式应用的例子包括将大型服务器裸片一分为二,使其作为单个处理单元运行。这类应用属于功能分割,在裸片间建立透明的数据隧道,要求Die-to-Die接口具备每秒数太比特的超高带宽。

另一个封闭式系统的例子是I/O芯粒连接到处理单元芯粒,或主计算裸片连接到AI加速器芯粒。在这种情况下,根据Die-to-Die适配器是否需要CRC或重传功能,可以使用串流FLIT或串流原生协议。串流原生和FLIT接口允许通过Die-to-Die接口连接供应商专有NoC,为系统连接提供了便捷路径,且无需在裸片间进行数据转换,实现了低延迟。串流FLIT模式将数据打包成上述6种FLIT格式之一,然后Die-to-Die适配器会添加CRC和标头字节,这实现了一种重传机制:数据在传输到Die-to-Die链路之前,先存储在缓冲区中。如果Die-to-Die通信检测到任何错误,则通过链路重新发送缓冲区中存储的数据,以实现无错通信。出于这些原因,系统可在不修改专有NoC的情况下利用Die-to-Die通信。

在非封闭式系统中,来自两个不同供应商的裸片可以进行互操作。使用不同来源的现成芯粒的开放生态系统方法是UCIe标准的最终目标。非封闭式系统中的每个裸片实现特定功能,以优化特定任务,通常需要低至中等的带宽。

由于在非封闭式应用中,两个裸片之间必须具备互操作性,因此使用PCIe和CXL等行业标准协议具有优势。这些标准协议具有软件和生态系统支持,便于不同代产品间的使用。需要时,CXL等协议还可实现两个裸片间的缓存一致性。例如,一个供应商的计算裸片可与另一个供应商的加速器裸片进行互操作。

还有其他一些应用也需要Die-to-Die连接。

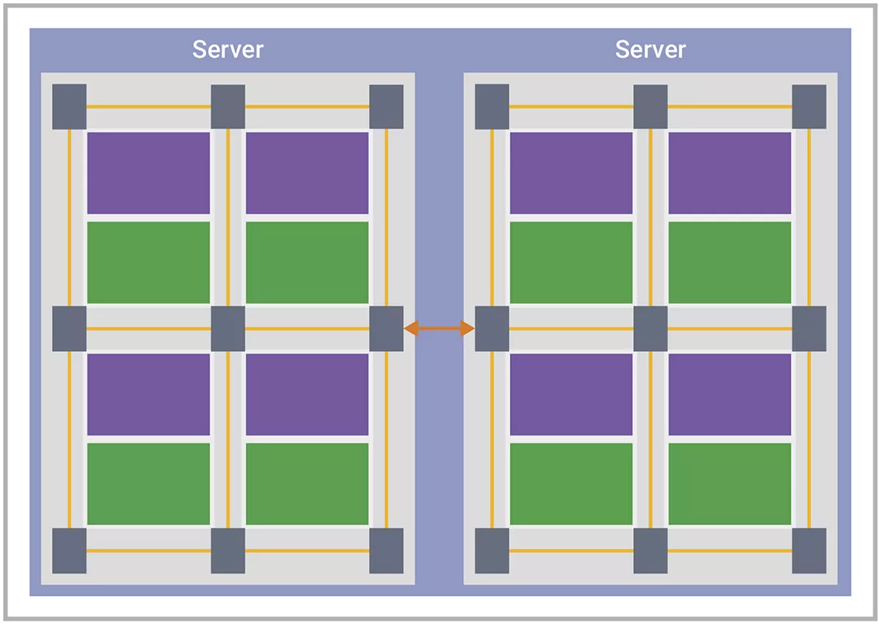

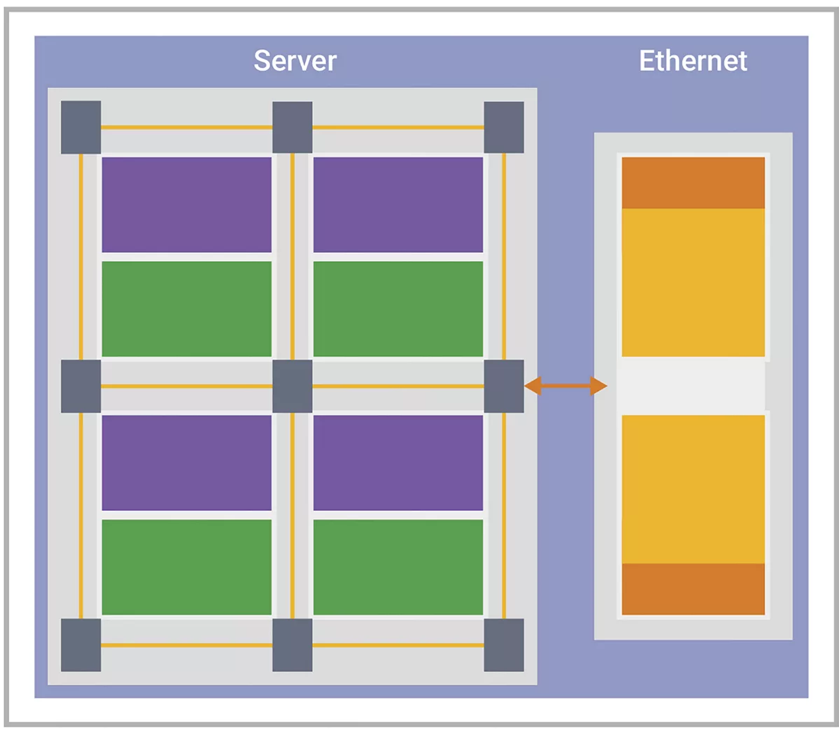

图2所示的第一种应用是服务器或计算裸片,Die-to-Die互连两侧均为同构裸片。这些芯粒需要低延迟的NoC到NoC接口。如果需要一致性,可使用CXS;如果不需要一致性,则可使用AXI。CXS接口以CXS信号格式(可以是CCIX 2.0或来自SoC应用的CHI)接收数据,并将其转换为FLIT格式。例如,新思科技UCIe控制器的CXS接口使用68B FLIT格式2处理CCIX 2.0数据,使用256B延迟优化的FLIT格式6处理CHI数据。类似地,AXI接口可以接收AXI4/AXI3接口信号,并将其转换为FLIT。这些接口直接连接到SoC NoC,实现两个裸片间的流量传输。该接口可以是用户定义或专有的,此时开发者可以使用UCIe Die-to-Die适配器的串流原生或串流FLIT接口。

图2:两侧具有同构裸片的服务器芯片示例

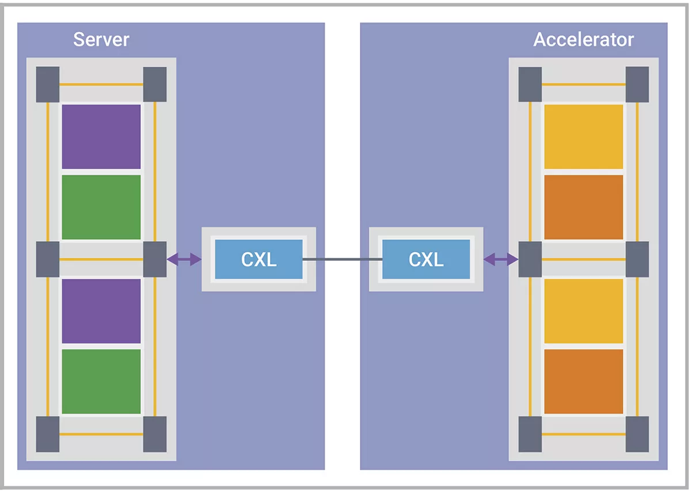

如图3所示,第二种应用是将计算裸片连接到加速器芯粒。接口协议通常要求低延迟和一致性,有时还面向开放的芯粒市场。在此类应用中,开发者可以依赖CXL或PCIe等协议实现互操作性,若两侧裸片来自同一供应商,也可以利用UCIe串流接口。

图3:两侧分别为服务器和加速器芯粒且利用CXL协议

图4展示了裸片分割的应用场景,其中带有以太网或PCIe的IO芯粒连接到计算芯粒。这些应用主要为封闭式,可使用串流原生或串流FLIT接口。如果服务器裸片上的NoC也使用AXI,还可以使用AXI接口。

图4:IO芯粒与计算裸片通过串流接口进行互操作

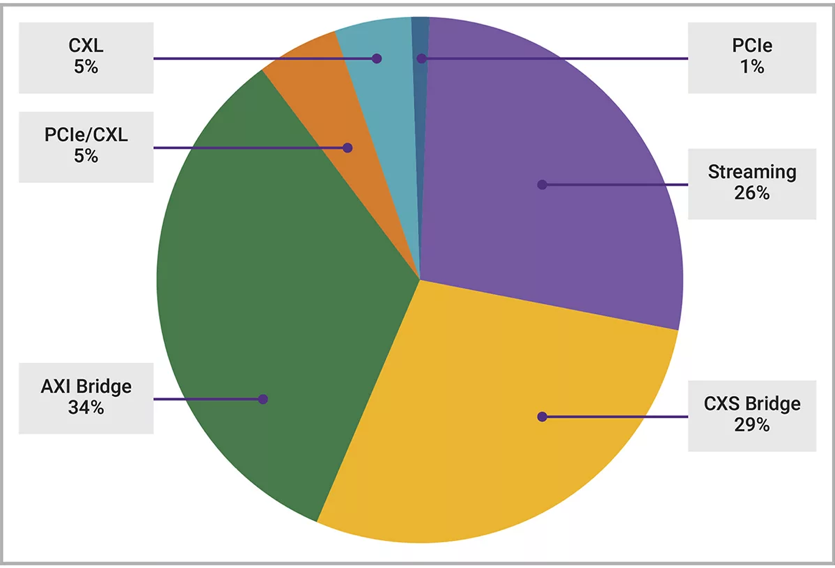

如今,大多数Multi-Die设计采用封闭式裸片,高性能计算(HPC)和人工智能(AI)是此类Multi-Die设计的主要应用领域。

如图5所示,AXI是当今大多数Multi-Die设计中主要的SoC NoC接口之一。CXS接口广泛用于Arm NoC,可支持缓存一致性。新思科技UCIe控制器支持CXS接口,有助于通过互连传输CHI C2C数据。新思科技的控制器经过优化,可与Arm NoC和Arteris IP NoC进行互操作。市场上的其他设计主要根据具体应用采用串流原生或FLIT接口,从而在裸片间提供最低延迟接口。在需要标准化的应用中,也会采用PCIe和CXL协议。

图5:NoC接口的使用情况细分

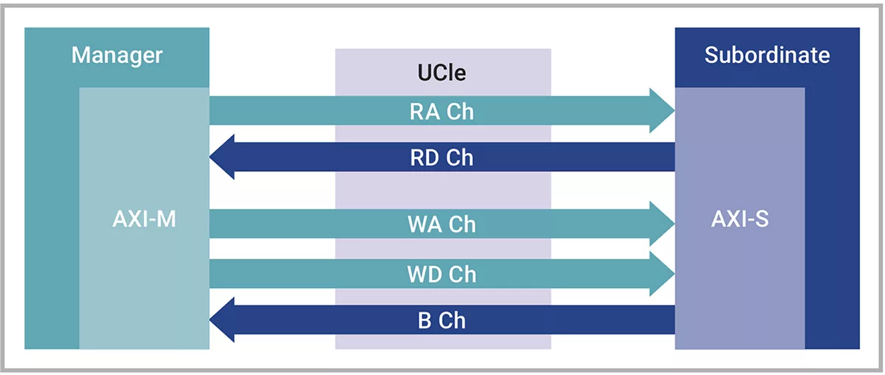

AXI在主设备和从设备之间提供单一接口。如图6所示,每个AXI通道仅能单向传输信息。该架构不要求通道之间存在固定关系,因此各通道可视为相互独立。

图6:AXI接口通道概述UCIe规范层

UCIe Die-to-Die适配器的接口只是一个隧道接口,可将数据从一个裸片中的AXI接口(主设备或从设备)传输到另一个裸片中的另一个AXI接口(从设备或主设备),而不会对数据进行任何形式的处理。实现AXI接口的UCIe串流FLIT采用UCIe标准定义的重传机制。启用重传机制时,UCIe可提供点对点的无损数据通信通道。开发者可选择使用任何一种已定义的FLIT格式来实现。

例如,新思科技的AXI实现使用FLIT格式2或6。如果需要较低延迟,可以使用串流FLIT格式2传输AXI信息,但与串流FLIT格式6相比,UCIe引入的带宽开销更高。如果需要更高带宽,可以使用串流FLIT格式6来传输AXI信息(此时延迟更高)。将AXI数据打包成FLIT是一种专有实现方式,要求Die-to-Die互连两侧都具备该实现,以便以与初始打包相同的方式检索另一裸片上的AXI数据。这导致在使用AXI接口进行Die-to-Die连接时存在局限性,不同供应商在基于UCIe的Die-to-Die互连上实现AXI时无法进行互操作。这一局限性在行业内所有基于UCIe实现AXI的供应商中普遍存在。

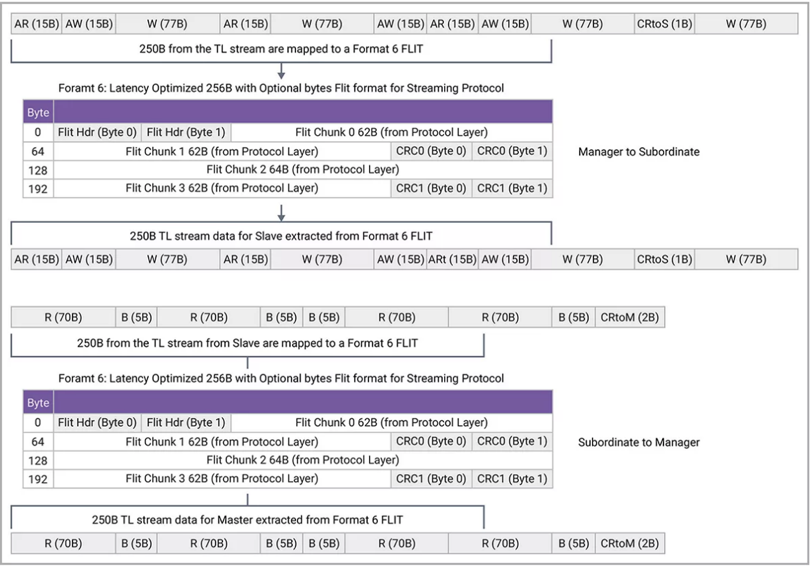

图7展示了新思科技AXI实现的一个示例,来自不同地址的连续单独读写(无突发)映射到FLIT格式6。不同的读写请求通过读地址、写地址和写数据通道从AXI主设备发送到从设备,并被打包成FLIT。图7的下半部分展示了从设备对主设备读写请求的响应。

图7:新思科技AXI实现的一个示例,来自不同地址的连续单独读写映射到FLIT格式6

在有效载荷、标头和CRC数据字节方面,对于68B串流FLIT格式2和256B串流FLIT格式6,UCIeFLIT打包效率分别为94.11%和97.65%。在AXI的每个通道中,写数据通道包含多个信令数据。存在写数据通道、写有效信号、带写有效和写就绪的写结束信号等。总体而言,在AXI事务中,由于来自不同AXI通道的FLIT中包含额外数据,实际数据有效载荷的效率较低。

结语

新思科技提供包括PHY、控制器和验证IP的完整UCIe IP解决方案。作为Multi-Die设计领域的领导者,新思科技推动合作以促进创新。新思科技UCIe PHY IP支持在最先进的工艺和封装技术上实现16G、32G、40G和64G的数据速率。新思科技UCIe控制器支持串流原生、串流FLIT,以及AXI、CXS、CHI C2C等接口和PCIe、CXL等协议。新思科技与Arm和ArterisIP等行业标准NoC供应商合作,确保系统的互操作性和高性能,简化了客户的实现过程。