展位信息

爱德万测试:A14

展会地点:上海嘉定喜来登大酒店

(嘉定区菊园新区嘉唐公路66号)

展会时间:2025年8月5-7日

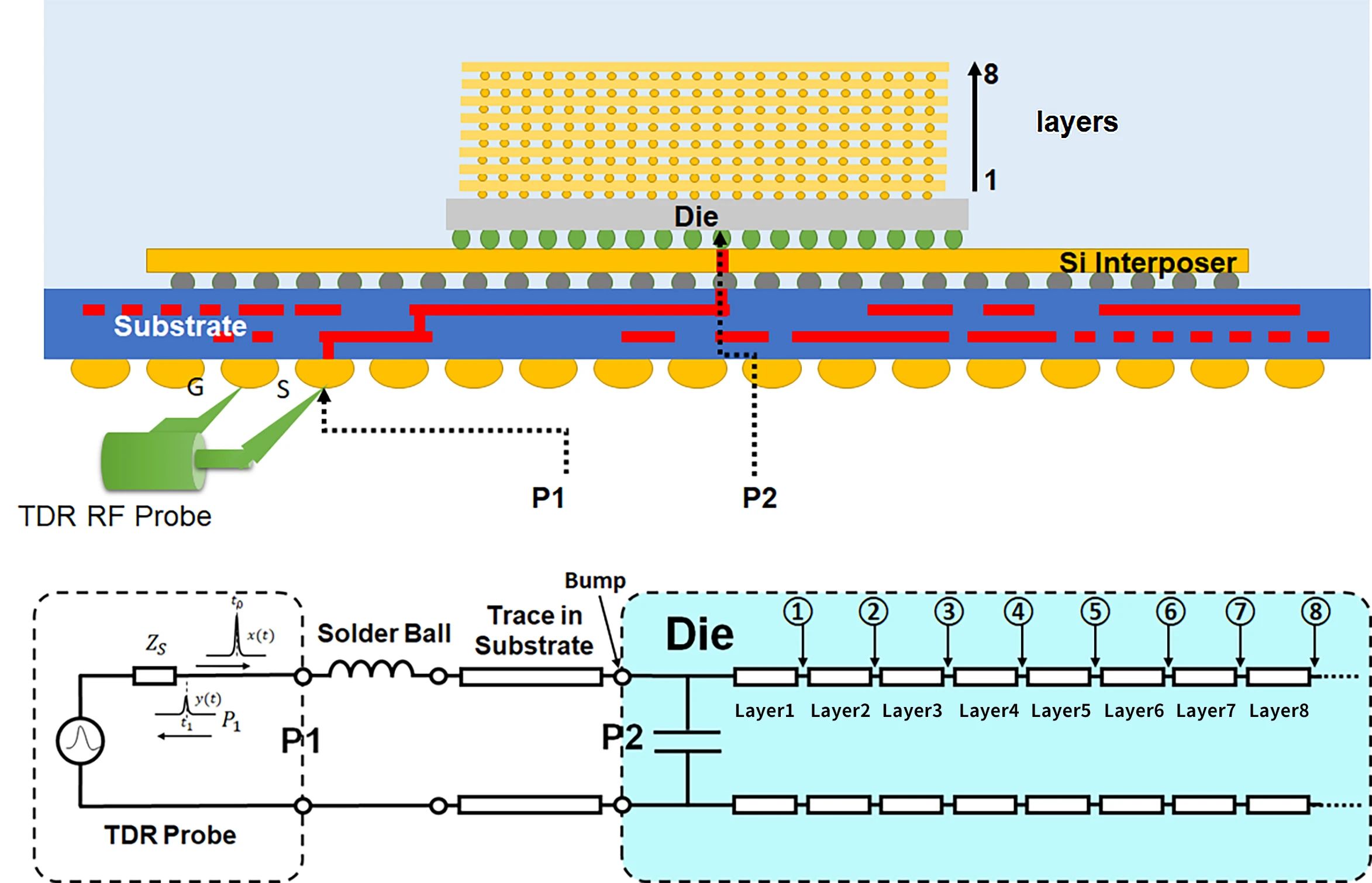

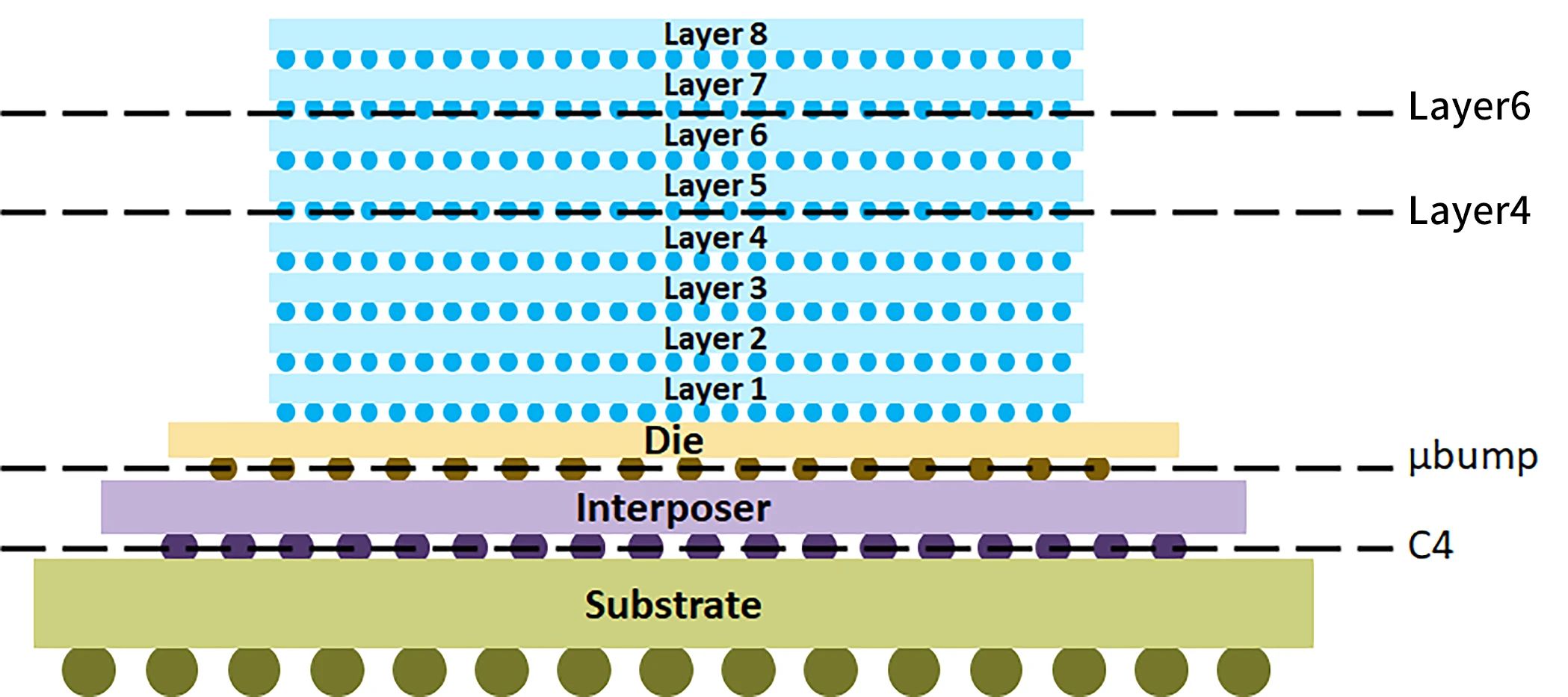

随着3D先进封装芯片内部结构日益复杂,密度高、结构精细的特征使封装级失效点隐蔽多样,增加了封装级失效分析难度。

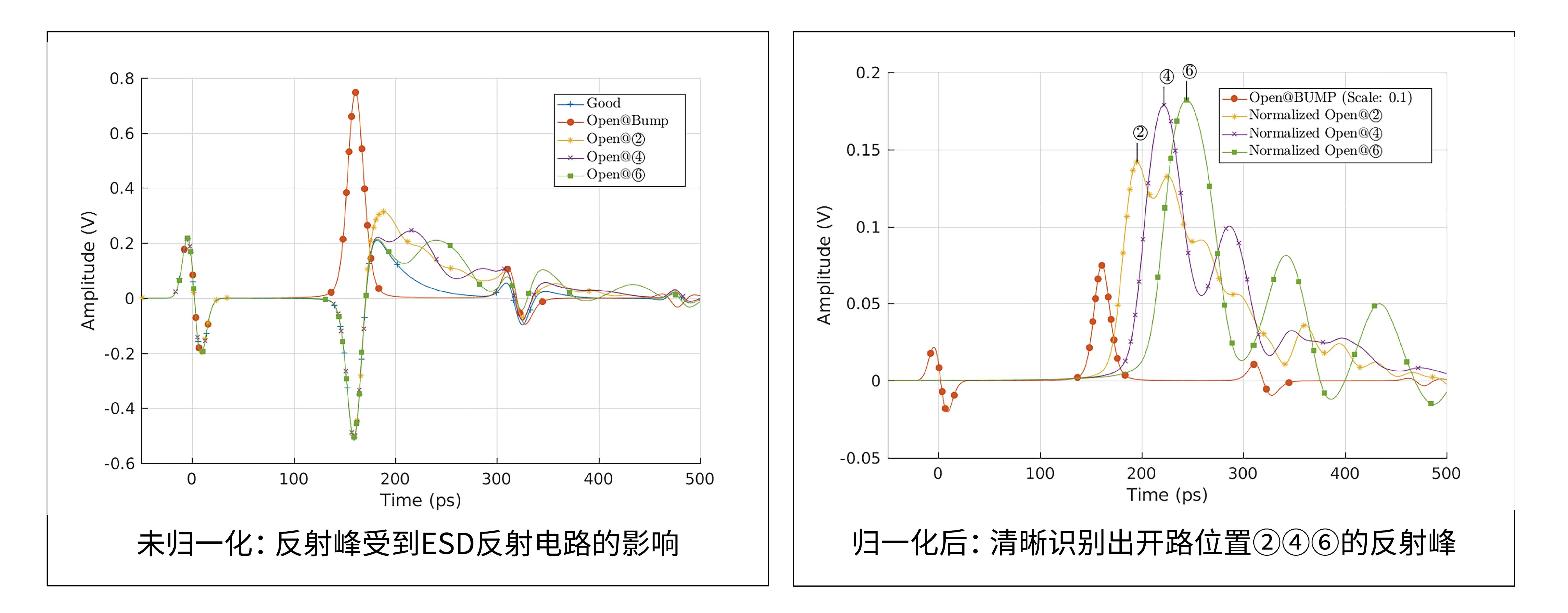

ESD电容引起的强衰减,信号幅度降低,失效难以识别,无法直接检测Die内部失效

爱德万测试TS9001TDR创新性地融合时域反射技术与仿真分析,精准定位封装级失效,推出两大核心检测方法:

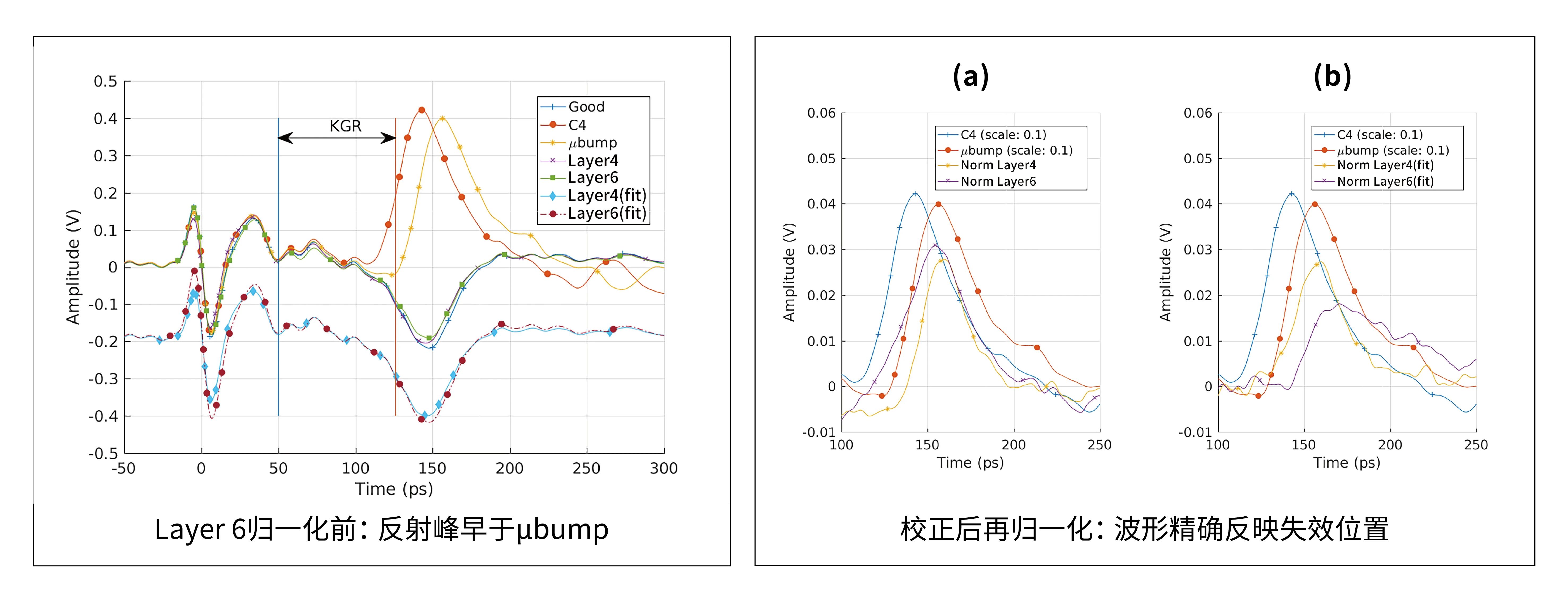

波形归一化(Normalization)

与良品波形进行归一化,消除ESD影响,突显失效点的时域反射

近芯片校正(Near-Die Correction)

焊球到微凸点之间路径长度不一致,工艺公差导致波形幅度/时间偏移

定义KGR(已知良区),进行如下最小二乘校正

校正后再归一化→消除样本差异,提高识别精度