近日,美国财政部长贝森特在《All In Podcast》节目中表示,台积电斥资 400 亿美元在亚利桑那州兴建的大型晶圆厂,可能仅能满足美国 7% 的半导体需求。他指出,台积电在当地面临监管障碍与繁琐程序,导致这座 400 亿美元的晶圆厂建设进度放缓。贝森特批评道,“芯片厂建设速度过快,计划频繁变更,监管人员会因此要求停工。” 他还感叹,美国的建设环境因各种法规变得极为艰难。

台积电作为全球最大的晶圆代工厂,是英伟达、苹果等企业的关键供应商,目前正加速推进亚利桑那州的扩建计划。该公司计划其第二座工厂于 2027 年前投产,并预计其先进的 2 纳米产能的 30% 最终将来自亚利桑那州工厂。然而,贝森特认为,环境法规已导致美国去工业化,要促进建设,必须降低监管门槛。

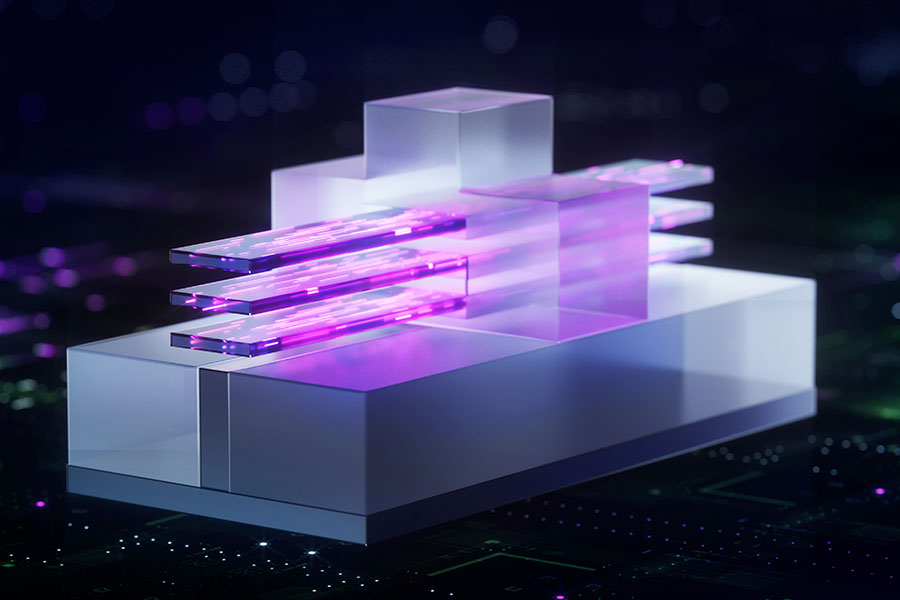

尽管在美建厂面临挑战,台积电在先进制程领域的技术进展仍处于行业领先地位。台积电计划今年下半年量产 2 纳米制程,其量产曲线预计与 N3 制程相似。此外,台积电最先进的 A14 制程技术开发进展顺利,计划于 2028 年量产,并将在 2029 年推出采用超级电轨的版本,进一步强化该制程技术。

台积电表示,受智能手机与高性能运算(HPC)应用的推动,预计 2 纳米制程技术在量产的前两年,产品设计定案数量将超过 3 纳米和 5 纳米制程同期水平。相较于 N3E 制程,2 纳米制程在相同功耗下速度可提升 10% 至 15%,相同速度下功耗可降低 25% 至 30%,芯片密度增加超过 15%。

此外,台积电还规划了后续的 N2P 制程技术,该技术在 N2 制程的基础上,将为智能手机与 HPC 应用提供更优的效能和功耗表现,计划于 2026 年下半年量产。依照台积电的技术蓝图,后续还将推出采用超级电轨(SPR)的 A16 制程,相较于 N2P 制程,A16 制程在相同功耗下速度可提高 8% 至 10%,相同速度下功耗降低 15% 至 20%,芯片密度提升 7% 至 10%,计划于 2026 年下半年量产,将成为 HPC 产品的理想解决方案。