氮化镓(GaN)基电子器件凭借高频、高效、耐高温及抗辐射等卓越特性,已成为下一代高效电力电子与射频电子系统的核心支撑器件,在5G/6G通信、智能消费电子等领域展现出显著优势。然而,由于外延衬底与GaN基外延层之间存在严重的晶格失配和热失配,GaN基异质结构外延薄膜中不可避免地存在高密度线性位错(约10⁸ cm⁻²),这一数值远高于Si和SiC等传统半导体材料。这些位错引起的漏电与可靠性退化问题,成为限制GaN基电子器件向更高电压和更大功率应用拓展的关键挑战。

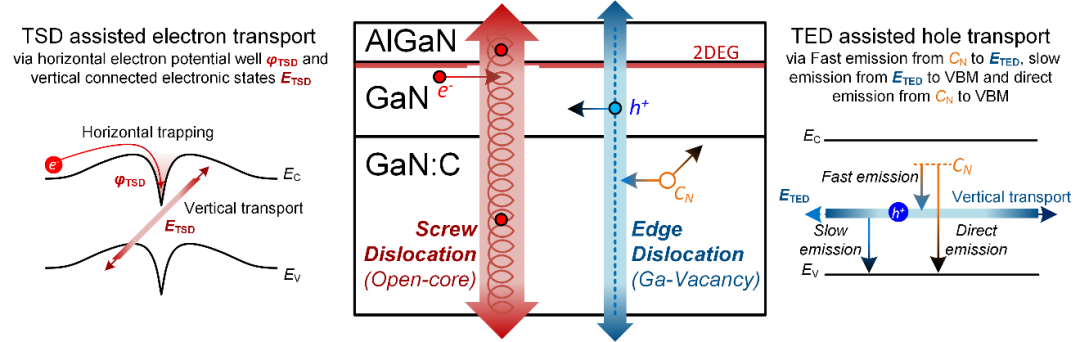

针对这一技术难题,中国科学院微电子研究所GaN基功率电子器件研发团队联合北京大学、香港科技大学、剑桥大学、武汉大学、中国科学院半导体所和苏州能讯高能半导体有限公司等单位,首次明确阐释了GaN异质外延中不同类型位错对器件性能的影响机理。研究团队创新性地构建了"双通道位错输运"模型,揭示了GaN外延层中螺位错和刃位错分别作为电子与空穴的独立传输路径,对器件漏电和动态电阻退化产生截然不同的影响。

研究团队运用课题组自主开发的创新模式深能级瞬态谱测试系统、低温光致发光、导电/电势原子力显微镜等多种先进表征方法,结合第一性原理计算,从原子层级深入剖析了位错的微观机制。研究发现,螺位错在其开核侧壁诱导形成纵向连通的超浅能级电子态,同时在位错核心区域形成电子势阱,构成贯穿外延层的"电子通道";而刃位错则在周围诱导形成连续分布的空穴陷阱,这些陷阱与碳掺杂GaN缓冲层中的CN型缺陷耦合,形成"空穴通道"。

在650-V级GaN基HEMT器件上的电学测试进一步验证了这一理论。研究表明,即使总位错密度较低,螺位错主导的器件在高压开关应力作用下,其动态导通电阻退化幅度显著高于刃位错主导器件。这一现象证实了螺位错易导致电子泄漏、电荷堆积与电流崩塌,而刃位错辅助的空穴再分布则有助于缓解缓冲层电子积累,从而减轻动态性能衰退。

这项研究启示我们,通过外延工艺调控螺位错与刃位错的比例,有望在保持整体晶体质量的前提下,实现GaN功率器件在漏电与动态可靠性之间的最优平衡。该成果为GaN器件中的"缺陷工程"开辟了新思路,创新性地提出将位错视为可工程化的一维载流子管道,而非单纯的有害结构缺陷。这一策略有望推广至其他半导体材料体系,为构建"位错电子学"理论体系奠定基础。

相关研究成果以"Dislocation-Assisted Electron and Hole Transport in GaN Epitaxial Layers"为题发表在Nature Communications上。中国科学院微电子研究所姚毅旭助理研究员为论文第一作者,黄森研究员、刘新宇研究员、北京大学沈波教授和香港科技大学Kevin J. Chen教授为论文的共同通讯作者。该研究得到了国家自然科学基金重点、面上及青年基金项目,中国科学院-香港裘搓基金以及"中国科学院微电子研究所-香港科技大学微电子联合实验室"等项目的资助。

【图1】GaN外延中位错电子-空穴双通道输运模型:电子在螺位错(TSD)辅助下,经由ETSD浅电子能级和φTSD电子势阱共同作用实现输运;空穴则在刃位错(TED)的辅助下,于刃位错引入的能级ETED与碳掺杂引入的碳替氮位CN之间通过快速、慢速和直接发射三类路径完成输运。