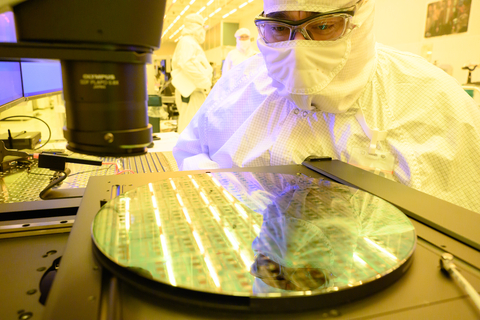

半导体行业几十年来一直依靠平面缩放来提高性能,但这种方法已经面临物理极限。随着人工智能应用需求不断增长,英特尔、台积电和三星等主要晶圆厂正在研发全面解决方案,为下一代计算设备提供支持,3D IC成为半导体大厂布局的重点。

AI应用加速3D IC开发进程

3D IC是通过垂直堆叠芯片并利用 TSV(硅通孔)实现更高密度的三维集成技术。与当前主流的先进封装技术,如 2.5D 封装、Chiplet、扇出型封装等,同属于后摩尔时代提升芯片性能的关键技术。3D IC 是先进封装技术中垂直集成的极致体现,通常面向更高性能的计算场景。其他技术相对更注重灵活性与成本平衡。

一直以来,各大半导体厂商都在开发3D IC相关技术。不过近年来掀起热潮的AI大模型却是真正意义上的全芯片堆叠技术蓬勃发展的最重要契机。台积电业务发展与全球销售高级副总裁张晓强表示:“晶体管技术和先进封装集成必须齐头并进,才能为客户提供完整的产品级解决方案。3D架构技术组合对我们而言已经变得至关重要。”

英特尔代工高级副总裁兼总经理Kevin O’Buckley也表示:“每个人都在谈论内存墙问题。随着我们不断增加内核数量,并将计算性能推向更高水平,首要任务就是满足数据处理的需求。3D就是一个例子,我们可以利用芯片面积的很大一部分来放置SRAM,而无需牺牲那些仍然需要用于计算的芯片面积。”

解决工艺材料核心问题

3D IC是利用垂直方向的空间来堆叠和互连多层电子元件。这种方法固然显著缩短了元件之间的物理距离,从而提高了芯片性能,降低了功耗,并缩小了尺寸。但是子系统的需求也更加复杂,在制造工艺、材料科学和设计方法都面临新的挑战。

TSV是3D堆叠的重要技术方向之一,其工艺直接影响互连密度与良率,需要突破更高的深宽比极限。在刻蚀工艺上,更先进的等离子刻蚀技术不断涌现,能够实现更高的深宽比和更精确的孔形状控制,满足日益小型化芯片的需求。在填充材料方面,除了传统的铜,新的低电阻、高可靠性导电材料正在研发与应用,如一些合金材料和碳纳米管复合材料等,有望进一步降低信号传输损耗。

芯片对芯片键合技术对于实现 3D 集成中芯片间的可靠性连接也至关重要。当下,芯片对芯片键合技术的研究重点集中在提高键合精度、速度与可靠性上。键合技术实现芯片间物理与电气连接,向无凸点、高密度演进。

台积电:基于 SoIC 的系统级整合

台积电一直在积极开发3D-IC的各种集成策略,近年来逐渐形成以SoIC(System-on-Integrated-Chip)为核心、结合CoWoS(Chip-on-Wafer-on-Substrate)和硅光子技术的完整技术体系,覆盖从逻辑堆叠到异构集成的全链条。

作为 SoIC 首发客户,AMD 将 MI300 的 CPU、GPU 和 HBM 通过 SoIC 与 CoWoS 结合,实现带宽超 5TB/s 的 AI 芯片。台积电业务发展和全球销售高级副总裁Kevin Zhang强调:“晶体管技术和先进封装集成必须齐头并进,才能为客户提供完整的产品级解决方案。3D fabric技术组合对我们变得非常重要。”

台积电正开发SoIC 2.0,目标将互连节距从当前的9μm 进一步缩小至5μm,并引入背面供电(BSPDN)技术,提升电源效率和散热能力。

台积电还在研发将硅基光电子集成到3D-IC设计中,以提高信号效率。台积电的COUPE(紧凑型通用光子引擎)平台可将电子芯片与光子芯片垂直堆叠,通过硅光子技术实现光信号直接输入芯片,功耗较传统电互连降低10 倍以上。

英特尔:Foveros 3D 封装的量产与升级

英特尔在 3D IC 领域的开发进展已形成以Foveros为核心、结合EMIB和PowerVia技术的完整技术体系,覆盖从逻辑堆叠到异构集成的全链条。Foveros 通过混合键合(Hybrid Bonding)和TSV(硅通孔)实现芯片垂直堆叠,支持逻辑芯片、存储芯片及光子芯片的高密度集成。

2024 年,Foveros 产能从 2023 年的2000片/月提升至4000-5000片/月,并计划 2025 年达到8000片/月。苹果已进入 Foveros 试产阶段,计划 2025-2026 年在Mac和iPad中量产,利用 3D 堆叠降低功耗和成本。

英特尔正开发Foveros 2.0,目标将互连节距从当前的 9μm 进一步缩小至5μm,并引入背面供电技术,提升电源效率和散热能力。英特尔也在积极开发光连接技术,以增强3D IC产品的性能。

三星:X-Cube架构持续推进

三星在 3D IC 领域的开发以X-Cube为核心,覆盖从逻辑堆叠到异构集成。X-Cube 通过硅通孔和混合键合实现芯片垂直堆叠,支持逻辑芯片、存储芯片及光子芯片的高密度集成。TCB(热压键合)方面,25μm 微凸块间距已实现量产,I/O 密度较传统方法提升 2 倍,热阻降低 5%。HCB(混合铜键合)的4μm 微凸块间距已完成验证,I/O 密度提升 70 倍,功率降低 33%,计划用于未来的SF4/5节点的HPC芯片。

三星正在开发光学 I/O 技术,通过硅光子技术实现光信号直接输入芯片。其光子介质层集成,即在封装中介层嵌入光子链路,连接逻辑芯片与 HBM,已完成样品验证。

在热管理技术方面,三星正在开发微流体冷却技术,在芯片内部嵌入微米级冷却通道,散热效率较传统风冷提升3倍。

三星计划将 3D IC 与下一代制程(如 SF4X、SF2P)结合,以实现更好的协同效果。