中国上海,2025 年 7月 8日—楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布扩大与三星晶圆代工厂的合作,包括签署一项新的多年期 IP 协议,在三星晶圆代工厂的 SF4X、SF5A 和 SF2P 先进节点中扩展 Cadence®存储器与接口 IP 解决方案的应用范围。为深化持续的技术合作,双方将利用 Cadence AI 驱动的设计解决方案,结合三星先进的 SF4X、SF4U 和 SF2P 工艺节点,为 AI 数据中心、汽车(包括高级驾驶辅助系统,ADAS)以及新一代 RF 连接应用提供高性能、低功耗的解决方案。

Cadence AI 驱动的设计解决方案以及全面的 IP 与硅解决方案组合,可显著提升设计人员的生产力,并加快基于三星晶圆代工厂先进工艺的尖端系统级芯片、小芯片(chiplet)及 3D-IC 产品上市时间(TTM)。

“我们支持三星晶圆代工厂工艺节点上的各种 IP、子系统和小芯片(chiplet),最新签订的多年期 IP 协议进一步巩固了双方持续的合作关系,”Cadence 高级副总裁兼芯片解决方案事业部总经理 Boyd Phelps 表示,“通过将 Cadence AI 驱动的设计与硅解决方案同三星的先进工艺相结合,我们正在为双方的共同客户提供打造创新产品所需的前沿技术,助力其产品更快上市。”

三星电子副总裁兼代工设计技术团队负责人 Hyung-Ock Kim 补充道:“Cadence 从 RTL 到 GDS 的全套数字工具现已通过三星最新的 SF2P 工艺节点认证,支持 Hyper Cell 和 LLE 2.0 等先进技术。Cadence 还将与三星密切合作,利用 GPU 加速来支持模拟迁移、提升电源完整性,并改进 3D-IC 的热分析和翘曲分析。此外,Cadence 与三星晶圆代工厂签署的多年期协议将进一步扩展存储器和接口 IP 解决方案,巩固我们双方的合作伙伴关系。”

扩充 IP 协议

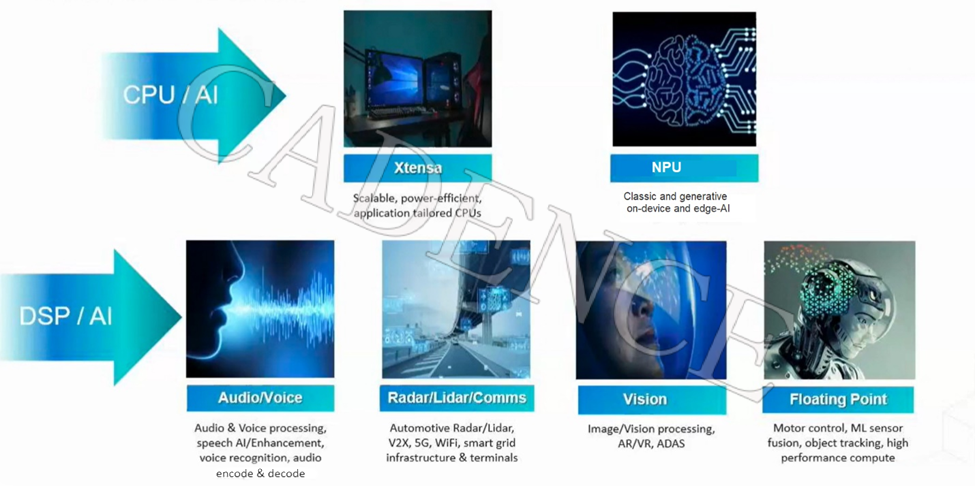

Cadence 与三星晶圆代工厂新签署了一项多年期协议,旨在为人工智能、高性能计算(HPC)和汽车应用提供先进的存储器与接口 IP 解决方案。扩展后的 SF4X IP 产品组合包含 LPDDR6/5x-14.4G、GDDR7-36G、DDR5-9600、PCI Express®(PCIe®)6.0/5.0/CXL 3.2、Universal Chiplet Interconnect Express™(UCIe™)-SP 32G 以及 10G 多协议 PHY(支持 USB3.x、DP-TX、PCIe 3.0 和 SGMII),配套的控制器 IP 可提供完整的子系统硅解决方案。专为汽车应用定制的 LPDDR5X-8533 PHY IP进一步完善了 SF5A IP 平台解决方案,而新增的 32G PCIe 5.0 PHY 补充了现有的 SF2P 产品,旨在满足领先 AI/HPC 客户的需求。

数字全流程认证与先进数字技术开发

基于广泛的设计与技术协同优化(DTCO)项目,Cadence 数字全流程已通过最新的三星 SF2P 工艺节点认证,包括三星 Hyper Cell 方法学。此外,Cadence 还实现了对三星Local Layout Effect(LLE)时序精度的支持。双方还就下一代工艺节点的 DTCO 项目展开合作。

Cadence Pegasus™ Verification System 已通过三星 SF2P 及其他三星节点的认证。Cadence 物理验证流程经过优化,依靠大规模可扩展性帮助双方的共同客户实现签核精度与运行时间目标,从而加速产品上市。

模拟设计迁移

Cadence 与三星晶圆代工厂成功实现了基于模拟单元的 4 纳米 IP 向先进 2 纳米工艺节点的自动化迁移,在保持功能与设计意图的同时实现更快的周转时间。此次迁移凸显了技术扩展与 IP 复用在节省时间与开发成本方面的重要性,并为未来跨不同工艺节点迁移模拟单元及其他 IP 奠定了基础。

射频芯片/封装协同设计参考流程合作

Cadence 与三星晶圆代工厂还基于三星 14 纳米 FinFET 工艺,成功展示了面向下一代毫米波应用的前端模块(FEM) /天线封装(AiP)协同设计完整流程。从初始系统级预算规划,到 RFIC/封装协同设计、分析及版图后验证在内的芯片/模块开发各个阶段的设计数据管理流程得到简化,加快了设计周转时间。

3D-IC 电源完整性

Cadence 与三星合作开发了覆盖全流程的 3D-IC 电源完整性分析方法,涵盖从早期探索到最终签核的完整流程,采用了先进的 Cadence EDA 工具,包括 Voltus™ InsightAI、Innovus™ Implementation System 以及 Integrity™ 3D-IC Platform。针对采用三星 SF2 工艺节点的高速 CPU 芯片,Voltus InsightAI 实现了 80%-90% 的 IR 压降违例修复,同时对时序和功耗几乎没有影响,充分展示了其平衡电源完整性与性能需求的能力。