7月3日—5日,2025第九届集微半导体大会在上海张江科学会堂盛大召开。本届大会以“张江论剑 共赢浦东 芯链全球”为主题,吸引了全球半导体产业领袖、技术专家和企业家齐聚一堂,共商行业发展大计。

国内集成系统设计EDA专家芯和半导体产品应用总监苏周祥受邀出席集微EDA IP工业软件论坛,并发表《集成系统EDA赋能加速Chiplet设计与仿真》主题演讲,介绍了在“AI驱动半导体设计变革“背景下Chiplet先进封装发展的最新趋势与挑战,并重点阐述了芯和半导体如何凭STCO集成系统设计理念、为Chiplet先进封装技术带来设计仿真端到端流程EDA解决方案。

芯和半导体产品应用总监 苏周祥

AI驱动芯片设计变革:算力爆发催生Chiplet革命

大会上,苏周祥指出:AI模型的持续迭代使得应用从云端向终端渗透,推动算力成为“第四类基础资源”。数据显示,英伟达AI算力8年提升超1000倍,HBM4传输速率达8Gb/s;2026年全球数据中心耗电量将接近日本全年用电量。传统SoC芯片面临性能、存储、功耗等“多重高墙”,而Chiplet异构集成技术成为破局关键——预计2030年3D封装晶体管规模将超万亿(达传统SoC单片数量的5倍),芯片尺寸极限提高至4~6倍光罩面积。

苏周祥以当前市场上搭载NPU(神经网络处理单元)模块的AI PC为例, 认为AI算力模块正加速下沉到终端设备,但杀手级应用仍有待深入挖掘客户需求进行开发。当前在HBM、LPDDR5X、电力供给等环节,业界已在持续推动性能突破。

Chiplet先进封装的设计困局:设计复杂度与多物理场协同仿真挑战

变革往往同时带来机遇与挑战。Chiplet先进封装设计就面临设计复杂度呈指数级攀升等难题。“集成芯粒数量剧增,迭代周期缩短至年级单位。” 以AMD针对2.5D/3D架构推出的“一年一迭代”的产品升级策略为例,其2025年即将发布的3nm制程MI350加速器通过10个以上Chiplet的异构集成和超过10,000条高密度互连走线实现性能突破,标志着先进封装技术已步入超大规模系统级整合阶段。

苏周祥强调,2.5D/3D堆叠技术因总热功耗增加、热分布不均、封装导热不畅等问题,同时又存在复杂的多物理场耦合效应,给热设计管理提出了更高的要求。传统EDA工具难以支持系统级分析流程、大容量仿真规模和高精度高效求解需求,亟需市场提供新的设计分析平台,统一架构布局与多场仿真&系统验证的双项目任务管理,提高芯片设计的优化迭代效率。

基于STCO构建,芯和针对Chiplet封装量身打造集成系统EDA平台

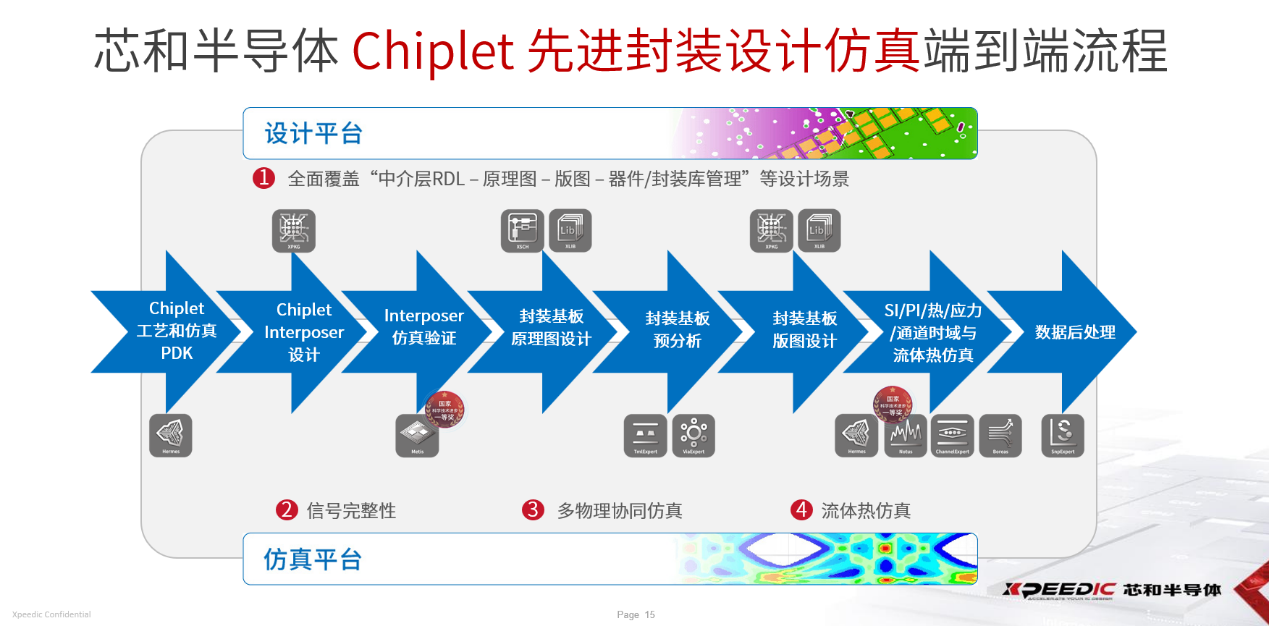

针对这些挑战,芯和半导体基于STCO集成设计理念,推出覆盖Chiplet先进封装全流程的EDA平台,主要功能包括:

设计端到端覆盖:支持从中介层RDL布线、原理图设计、版图优化到封装库管理的全链路设计闭环;

多物理场协同仿真:

提供Chiplet工艺PDK与跨尺度电磁仿真(SI/PI);

实现电-热-应力耦合分析与流体散热仿真(CFD);

支持Interposer及封装基板的多场景验证与后处理优化;

云端高效赋能:通过智能布线引擎与集群加速,提升仿真效率10倍,动态优化高功耗设计。

构建系统级EDA生态,赋能AI硬件落地

苏周祥进一步介绍,芯和半导体的EDA工具现已广泛服务于国内外领先的芯片设计企业和系统厂商,主要优势包括:

1. 自主研发的高精度求解器:完全自主知识产权的高精度求解器;

2. 模型接口丰富:支持多种版图文件格式导入和布线分析模板,支持多物理环境下电/热/结构属性设置;

3. 高效高质量网格剖分:支持2D/3D/六面体/三棱柱网格类型和自动化的 Speed/ Accuracy 剖分策略;

4. 丰富的后处理:集成多种标准接口(HBM/PCIe)协议规范,可自动生成分析报告和加载历史结果;

5. 一体化设计仿真平台:支持接入芯和电子系统设计仿真体系,帮助用户基于 STCO 理念构建一站式端到端的产品研发流程与平台;

最后,苏周祥强调,芯和半导体将持续深耕集成系统EDA领域,致力于打造“芯片—封装—板卡—机架—数据中心集群”的AI硬件系统端到端设计仿真EDA解决方案,助力全球AI硬件系统的高效落地。“我们将持续深化全栈仿真能力,构建面向AI Chiplet的EDA全流程工具链,加速生态协同创新。”