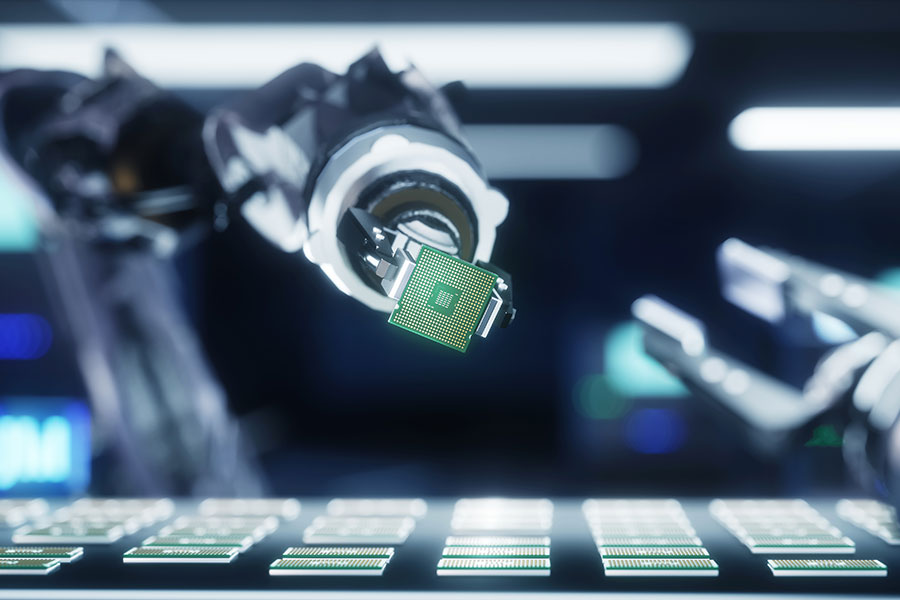

日本东京科学研究院(Science Tokyo)的研究团队提出了一种名为BBCube的创新性2.5D/3D芯片集成方案。

传统的系统级封装(SiP)技术采用焊球将半导体芯片二维(2D)排布,存在尺寸限制,因此急需发展新型芯片集成技术。针对高性能计算(HPC)需求,研究人员通过采用3D堆叠计算架构开发了新型供电技术,该架构将处理单元直接堆叠在动态随机存取存储器(DRAM)上方,标志着3D芯片封装领域的重大突破。

为实现BBCube技术,研究人员开发了涉及精密高速接合与粘合材料的关键技术。这些新技术能同时满足高内存带宽、低功耗以及降低供电噪声的高性能计算需求。

由Norio Chujo教授、Takayuki Ohba教授及东京科学研究院集成研究所WOW联盟异质与功能集成部门其他科学家组成的研究团队,首先开发了 一种面朝下的晶圆上芯片(COW)工艺以规避焊料互连的局限。他们采用喷墨技术与选择性粘合剂涂覆方法,成功在300毫米晶圆上实现了芯片间距仅10微米、贴装时间短于10毫秒的不同尺寸芯片顺序接合。“我们已在晶圆上集成超3万颗不同尺寸芯片,在零脱落故障下提升了接合速度。”Norio Chujo教授解释道。

为确保COW工艺的精密性与高速性,研究团队重点解决了影响超薄晶圆多层堆叠的热稳定性问题。通过对化学特性的精心设计,他们开发出名为“DPAS300”的新型粘合材料,可同时适用于COW与堆叠晶圆(WoW)工艺。这种由有机-无机杂化结构构成的材料在实验中表现出卓越的粘附性与耐热性。

最终,为实现高内存带宽并提升BBCube的供电完整性,科学家采用3D xPU-on-DRAM架构并辅以新型电力分配通道:在xPU与DRAM间嵌入电容器、在晶圆上制作重分布层、在晶圆通道与DRAM划片线上设置硅通孔。“这些创新使数据传输能耗降至传统系统的1/5~1/20,同时将供电噪声抑制在50毫伏以下。”Norio Chujo教授强调了3D堆叠计算架构的优势。

东京科学研究院研发的这套3D芯片集成技术,或将彻底变革下一代计算架构。(校对/赵月)