导读

一种全新的芯片设计模式正在诞生。在中国科学院计算技术研究所与西南交通大学组成的联合团队探索下,利用中国科学院计算技术研究所自主研发的ChipGPT与LPCM智能体“参加”了“芯原杯”电路设计大赛。。最终,两支人机协同团队在初赛中拔得头筹。他们不仅率先完成了全部设计并通过了所有功能性验证,最终综合成绩在所有参赛队伍中也名列前茅,超越了超过90%由国内顶尖高校硕博研究生组成的精英团队。”

近日,在半导体行业享有盛誉的“芯原杯”电路设计大赛上,由中国科学院计算技术研究所与西南交通大学组成的联合团队,上演了一场别开生面的“人机协同”实战。

这并非简单的AI辅助设计,而是一次对芯片设计方法的深度重塑。团队成员通过操控中国科学院计算技术研究所自主研发的ChipGPT [1]和LPCM [2]芯片设计智能体,向一项复杂的工业级设计任务发起挑战。

最终,人机协同团队在初赛中取得第一名,并在决赛的高压竞争中,率先完成了全部设计、通过了所有功能验证,且综合成绩超越了超过90%由国内顶尖高校硕博研究生组成的精英团队。

这一进展,标志着AI赋能的芯片设计流程已经具备了强大的竞争力和实用性,也展示了一种全新的、高效的人机交互设计模式。

高规格赛场与工业级挑战

“芯原杯”电路设计大赛由国内领先的芯片设计企业芯原股份主办,竞赛拥有十年的悠久历史,是国内集成电路领域最具影响力的竞赛之一。大赛聚焦于当前全球大热的开源指令集架构RISC-V,旨在为产业发掘和培养具备创新与实践能力的顶尖人才。决赛阶段的参赛团队,大部分是来自电子科技大学、西安电子科技大学、西安交通大学等集成电路领域强校的硕博研究生,代表了该领域的后备精英力量。

本届决赛的赛题,是一项非常典型的芯片前端设计任务:用Verilog硬件描述语言,设计并实现一个高性能的RISC-V向量协处理器。这项任务的复杂性体现在多个维度:

·精密的硬件架构:需要设计包含32个128位宽向量寄存器的完整体系,并能根据控制信号动态支持int8/int32等多种数据类型。

·复杂的指令集实现:要求实现vxor.vv(向量异或)、vmacc.vv(向量乘加)、vredsum.vs(向量归约求和)等五条核心向量指令。

·严苛的PPA(功耗、性能、面积)约束:设计必须在800MHz的目标频率下实现时序收敛,且芯片面积不得超过50,000 um²。

面对这样一个涉及深刻领域知识、需要反复迭代优化的专业任务,这套人机协同的新范式展现出了强大的解题能力。

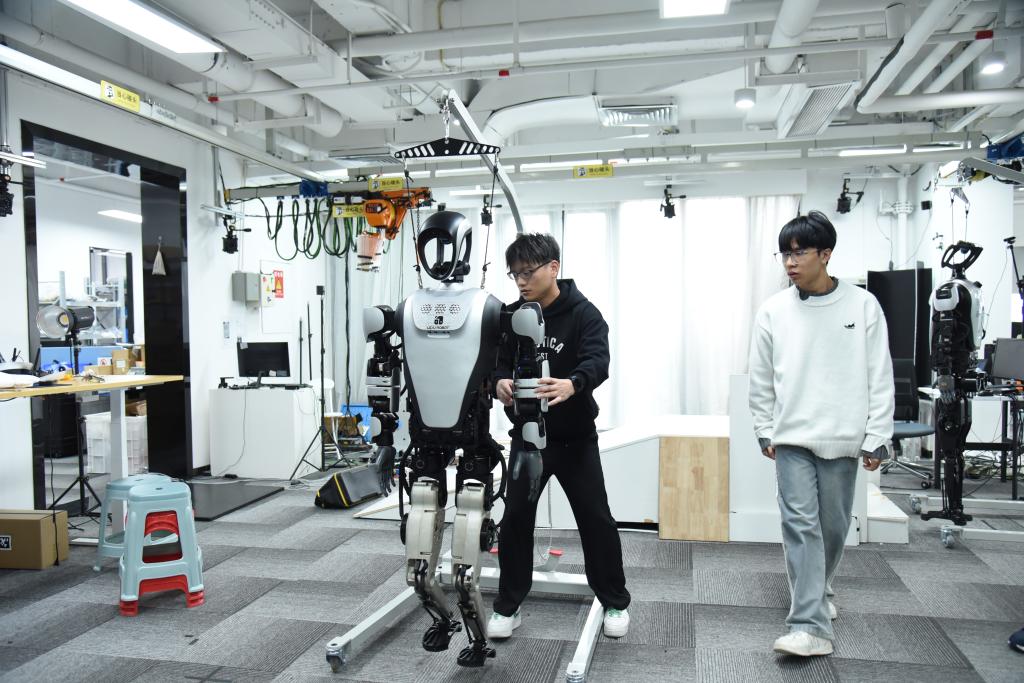

人机协同:工程师化身“智能体操控者”

本次参赛的两支队伍由中国科学院计算技术研究所和西南交通大学的成员联合组成,他们开创了一种全新的工作模式。

·队伍一:陈志榕(中国科学院计算技术研究所),常开颜(中国科学院计算技术研究所),马杰成(西南交通大学)

·队伍二:王坤(中国科学院计算技术研究所),李苍源(中国科学院计算技术研究所),黄巍霆(西南交通大学)

在比赛中,团队成员的角色不再是传统的RTL代码编写者,而是AI智能体的操控者和引导者。他们的主要工作是:理解设计规范,将其转化为高质量的Prompt(提示),输入给ChipGPT和LPCM智能体,然后由智能体生成所需的设计架构和Verilog代码。

这种模式下,工程师的核心价值从“如何实现”转向了“如何定义”,极大地提升了设计迭代的速度和创新的效率。

“芯”驰神往:AI大模型的技术积淀

卓越表现的背后,是中国科学院计算技术研究所ChipGPT团队在芯片大模型方向的持续深耕和多方面的技术研发。

在项目初期,研究团队也曾遇到过通用大语言模型(LLM)的瓶颈。虽然通用LLM能够生成语法上完美无瑕的Verilog代码,但它们普遍缺乏对硬件行为的深层理解,导致生成的代码在功能仿真中暴露出严重的功能性错误。

面对挑战,中国科学院计算技术研究所团队通过系统性的研发工作,在大规模集成电路设计上取得了突破。他们的研究成果涵盖了芯片大模型开发的多个关键环节,包括:

·构建高质量数据集:通过自动化的数据增强框架,从有限的样本中生成海量、高质量的训练数据。[3]

·硬件语言专属微调:针对Verilog等硬件描述语言的特性,对大模型进行深度微调(Fine-tuning),显著提升了模型在特定任务上的生成和修复能力。[3]

·融合领域知识与工具:探索将EDA(电子设计自动化)工具的反馈信息融入AI的设计流程中,让AI能够利用专业工具进行自我验证和迭代。[4]

正是这些在数据、模型、流程等多个维度的综合性技术突破,才共同铸就了今天ChipGPT和LPCM智能体在赛场上的卓越表现。

分秒必争:AI展现惊人效率

尤其值得一提的是,本次大赛要求所有参赛团队在短短两天内完成从设计、实现到验证的全部工作。

时间上的极端紧迫性,给所有人类选手带来了巨大压力,许多经验丰富的团队甚至都难以在规定时间内完成全部设计并成功交付。

然而,在这种高强度的环境下,由人机协同的两支队伍不仅保证了设计的质量与正确性,更是全场第一个 “交卷”的选手。这一方面展现了AI智能体解决复杂问题的能力,另一方面也凸显了人机协同模式在提升设计效率方面的巨大潜力。

在这个新范式中,AI将扮演“超级协作者”或“智能副驾”的角色,承担大量繁琐、耗时的底层编码、验证和优化工作,将人类工程师从巨大的工程负担中解放出来,从而能更专注于架构探索、功能创新等更具创造性的顶层设计工作,极大地提升整个团队的研发效率和创新能力。

参考文献

[1] Chang, K., Wang, Y., Ren, H., et al. (2023). Chipgpt: How far are we from natural language hardware design. arXiv preprint.

[2] Chang, K., Chen, M., Chen, Y., et al. (2024). Large processor chip model. arXiv preprint.

[3] Chang, K., Wang, K., Yang, N., et al. (2024). Data is all you need: Finetuning LLMs for Chip Design via an Automated design-data augmentation framework. In Proceedings of the 2024 Design Automation Conference (DAC).

[4] Li, C., Chen, C., Pan, Y., et al. (2025). AutoSilicon: Scaling Up RTL Design Generation Capability of Large Language Models. ACM Transactions on Design Automation of Electronic Systems.