AI热潮持续不坠,先进封装技术成为提升AI芯片效能的关键。继垂直堆叠的CoWoS封装后,可大幅提升芯片利用率的扇出型面板级封装(FOPLP)技术成为最新话题。群创董事长洪进扬接受中央社专访时透露,群创FOPLP今年一定会有具体的成果,并且出货,抢占全球半导体封装市场。

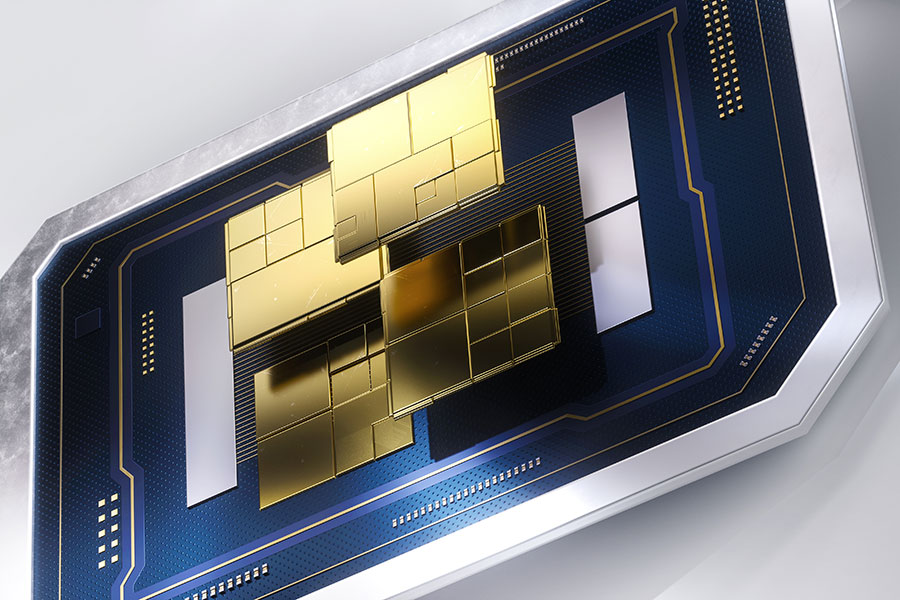

先进封装是指将不同芯片通过封装及堆叠技术整合在一起,以提升芯片效能、减少空间及功耗,如台积电积极投入的CoWoS技术。

而扇出型面板级封装(Fan-out Panel LevelPackaging,FOPLP)技术,因通过「方形」基板进行IC封装,可使用面积将较「圆形」晶圆大幅提升,使同样单位面积下,可摆放更多的芯片;方形基板利用率可达到95%,以3.5世代线FOPLP玻璃基板开发的中高阶半导体封装,可使用面积是12吋玻璃晶圆的7倍。

经济部2023年携手群创光电、工研院等厂商共同发表FOPLP成果,并进一步活化面板厂既有的旧世代产线,转型成具高附加价值的半导体封装产线,更具备「容纳更多的I/O数」、「体积更小」、「效能更强大」、「节省电力消耗」等技术及成本优势。

在经济部技术处A+计画支持下,群创已率先建置全球第一条由面板产线转型的FOPLP封装应用产线,跨足半导体先进封装领域;尽管FOPLP生产技术面临面板翘曲、均匀性与良率等问题,量产进度延宕,但群创与工研院持续合作减少面板翘曲量,让封装制程的破片与耗损降低。

洪进扬接受中央社专访时指出,两年前还没太多人讲扇出型面板级封装(FOPLP),但去年台积电董事长魏哲家在法人说明会表示,3年后将开始大量生产。有人质疑,群创凭什么跟台积电竞争,洪进扬表示,群创不是要跟现有半导体晶圆大厂、封装厂竞争,而是面板厂动线设计适合搬运玻璃基板。

他进一步指出,半导体晶圆封装改用方形的显示面板玻璃基板,若片数多、面积大可能需要机器搬运,既有的封装测试厂动线不会考虑到如何搬运玻璃基板;而面板厂原本的动线设计,早已规划好适合搬运玻璃基板。为避免运送过程易碎,可在群创继续进行下一阶段的封装制程,并可依客户需求,提供只钻好孔的玻璃基板或铺好线路的玻璃基板。

此外,扇出型面板级封装技术验证期,至少都要18个月以上,群创有现成的无尘室,可以顺利投入封装;封装厂若为了面板级封装盖一个无尘室太花钱,且需要时间兴建。

洪进扬强调,台积电是打算从300x300开始做,群创3.5世代线玻璃基板大小为620x750,只要1/4大小即足够应付首批的扇出型面板级封装需求。

未来若芯片厂商需要更大的可使用面积进行IC封装,洪进扬说,群创就通过「方形」基板把「海埔新生地」做出来,「你要新的土地,我就帮你找出来」,因为面板厂提供的玻璃基板面积够大,用3.5代厂就比现有晶圆封装的面积大,将来还可通过5代线、6代线提供更大面积的玻璃基板。

不过,洪进扬表示,群创在面板业领先,但在封装业却是新手。扇出型面板级封装是一种先进的技术,是很大的领域,有不同的技术主流,群创有必要做投资,进入市场先了解,先从相对简单的chip first(先放芯片再铺线路)的方案开始尝试,这个里程碑希望获得客户的认可,技术上已拿到客户的认证,量产时程尽快推进。

洪进扬透露,扇出型面板级封装今年一定会有具体的成果,并且出货,将持续精进技术及人才的培养。他认为,群创往扇出型面板级封装的技术、人力、资源发展,一定是对的方向。

他说,其他包括chip last或重布线(redistributionlayer,RDL)技术,以及最终极的导通孔玻璃晶圆(Through Glass Via;TGV)技术,不表示停下来不做了,因考量验证速度,并非所有技术都以量产为唯一检验标准,不同的技术有不同的里程碑在持续推进中。