全球顶尖的半导体研发机构imec首席执行官Luc Van den Hove表示,如果行业想要避免未来人工智能(AI)发展的瓶颈,就需要转向可重构芯片架构。

Luc Van den Hove表示,快速的AI算法创新速度超过了当前开发特定、注重原始功耗芯片的策略,导致能源、成本和硬件开发速度方面存在重大缺陷。专用集成电路(ASIC)可能需要一到两年的时间来开发,并需要六个月的时间在晶圆厂制造。

他表示:“存在巨大的资产搁浅风险,因为当AI硬件最终准备就绪时,快速发展的AI软件社区可能已经发生了变化。”

OpenAI等已经走上构建定制芯片的道路,以加速创新。然而,Luc Van den Hove表示,此举对大多数公司来说既危险又不经济。

数十年来,imec一直是全球领先的半导体研究中心,并与领先的半导体公司合作开展竞争前项目。这使得imec能够提出并评估许多目前处于前沿的技术,包括FinFET、全环绕栅极(GAA)晶体管、背面供电和Chiplet。这些突破性技术通常会在未来数年被台积电和英特尔等芯片制造商广泛采用。

随着AI行业从大型语言模型转向医疗或自动驾驶应用的代理AI(Agentic AI)和物理AI,Luc Van den Hove认为,未来的芯片将把所有必要的功能重新组合成称为“超级单元”的构建模块。

Luc Van den Hove表示:“可编程片上网络将引导和重新配置这些超级单元,使它们能够快速适应最新的算法要求。”

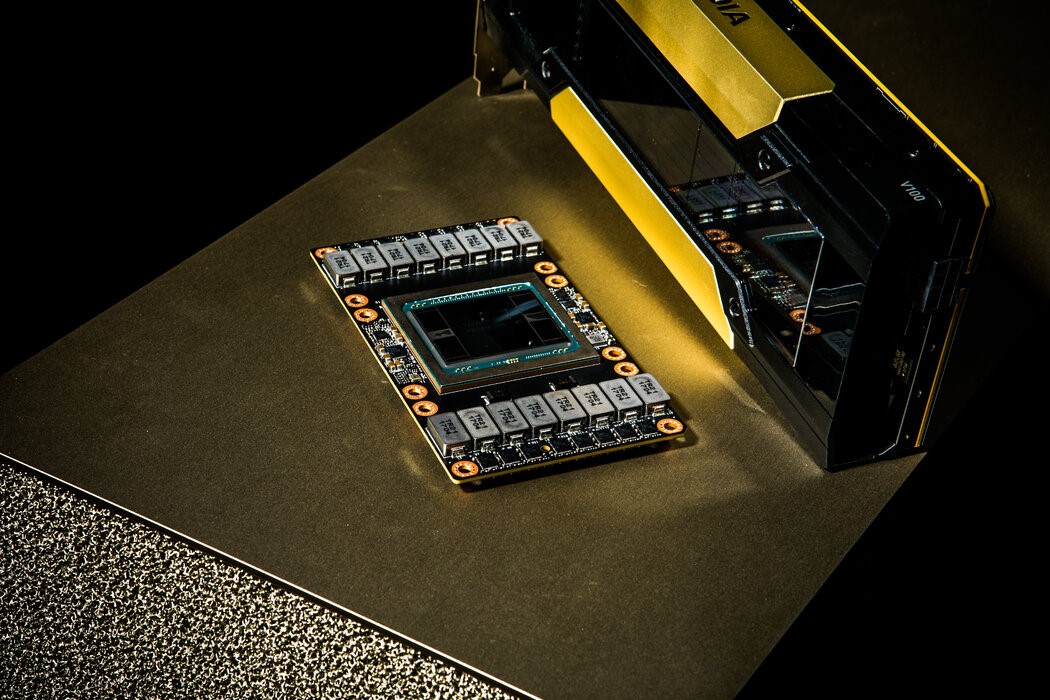

他补充说,这需要真正的3D堆叠,这是一种将逻辑层和存储硅片层粘合在一起的制造技术。

imec为3D堆叠技术的进步和改进做出了重要贡献,这项技术将应用于台积电A14(1.4nm)和英特尔未来的Intel 18A-PT(1.8nm)节点。

imec将于5月20日和5月21日在比利时安特卫普举办旗舰会议ITF World。(校对/赵月)