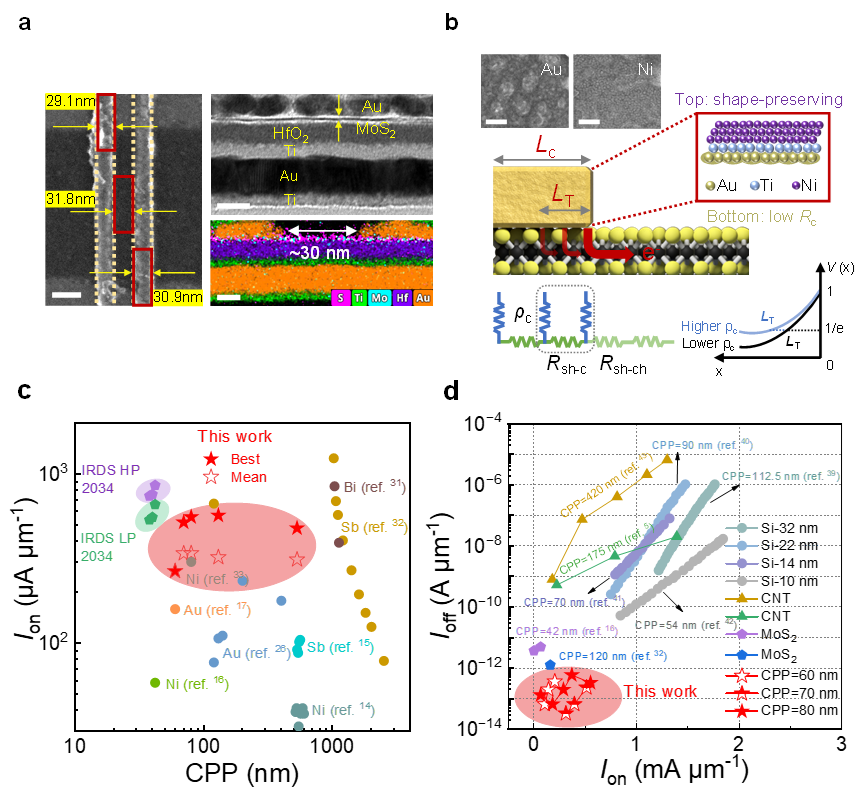

当半导体技术迈向后摩尔时代,晶体管接触多晶硅间距(Contacted Poly Pitch, CPP)作为衡量先进逻辑工艺节点的核心指标,正在重构芯片性能、功耗与集成度的三维博弈边界。CPP的全面微缩需要沟道长度和接触长度同步减小,然而,接触电极在小尺寸下的有效形成和电流拥挤现象导致的接触电阻骤增问题,成为制约器件极限微缩的关键挑战。此外,现有基于先进节点的新器件研究多聚焦于单器件层面的性能突破,鲜有涉及集成阵列的功能电路验证,而后者正是新器件能否从实验室走向产业(Lab-to-Fab),真正拓展硅技术的关键。

针对上述挑战难题,复旦大学微电子学院周鹏/王水源团队提出了一种兼具低接触电阻与保形作用的复合金属电极策略,突破二维晶体管接触长度微缩瓶颈,实现CPP全面微缩至60nm,不仅接近当前主流FinFET工艺的物理极限(TSMC N7节点CPP≈54nm),更获得了超节点性能,满足2034年国际器件与系统路线图(International Roadmap for Devices and Systems, IRDS)中先进晶体管的性能目标(0.7nm/A7节点)。

5月12日,相关成果以“Channel and contact length scaling of two-dimensional transistors using composite metal electrodes”为题发表于国际顶级期刊《自然-电子学》(Nature Electronics),DOI: 10.1038/s41928-025-01382-6。

沟道-接触全面微缩的器件表现出优异的电学性能,包括超过108的开关比,高达300μA μm-1(700μA μm-1 for CPP=80nm)的开态电流和低至1pA μm-1的关态电流,优于其他新型小尺寸晶体管技术(如CNT、MoS2 FETs)。进一步,团队构建了全面微缩的二维晶体管阵列,具有高良率和均一性,并验证了先进逻辑集成应用的可行性。这项研究成果不仅为实现二维晶体管尺寸和性能极限提供了新技术路径,更为后摩尔时代低功耗逻辑电路设计与实现提供了新范式。

CPP=60nm的全面极限微缩与超节点性能比较

复旦大学集成芯片与系统全国重点实验室、集成电路与微纳电子创新学院、微电子学院周鹏教授和王水源研究员为论文通讯作者,王水源研究员和博士生陈思凡为论文第一作者。研究工作得到了科技部重点研发计划、国家自然科学基金、上海市科委等项目的资助,以及科学探索奖的支持。